# TECHNICAL MANUAL

# SIGMA 3 CORE MEMORY

Specifications, equipment descriptions, and procedures contained herein are subject to change without notice.

**April 1973**

This publication supersedes 901594A dated August 1972

Prepared by Service Education & Performance

# TABLE OF CONTENTS

| Section | Title                                            | Page             |

|---------|--------------------------------------------------|------------------|

| I       | INTRODUCTION                                     | 1-1              |

|         | 1-1 Scope of Manual                              | 1-1              |

|         | 1-2 Content of Manual                            | 1-1              |

|         | 1-3 Related Publications                         | 1-2              |

|         | 1-4 Prerequisites to Manual Use                  | 1-2              |

|         | 1-5 Sigma 3 Core Memory                          | 1-3              |

|         | 1-6 Physical Description                         | 1-3              |

|         | 1-7 Basic Memory Unit (BMU)                      | 1-5              |

|         | 1-8 Core Diode Module (CDM)                      | 1-5              |

|         | 1-9 Core Drive and Sense Logic                   | 1-5              |

|         | 1-10 Memory Port Multiple (MPM)                  | 1-8              |

|         | 1-11 Capabilities                                | 1-8              |

|         | 1-12 Basic Memory System Expansion               | 1-11             |

|         | 1-13 Memory Address and Data Word Format         | 1-12             |

|         | 1-14 Memory System Power Requirements            | 1-12             |

|         | 1-15 Power Supplies                              | 1-14             |

| II      | FUNCTIONAL DESCRIPTION                           | 2-1              |

|         | 2-1 Introduction                                 | 2-1              |

|         | 2-2 Memory Port Multiple (MPM) Section           | 2-1              |

|         | 2-3 Address Decode-Reset Early-Port Select Logic | 2-3              |

|         | 2-4 MPM Timing and Control Logic                 | 2-4              |

|         | 2-5 Memory Address Register Logic                | 2 <del>-</del> 5 |

|         | 2-6 Current Direction and Memory Timing Logic    | 2-5              |

|         | 2-7 Memory Information Register Logic            | 2 <b>-</b> 6     |

|         | 2-8 Parity Bit Strobe Logic                      | 2-7              |

|         | 2-9 Basic Memory Unit (BMU) Section              | 2 <b>-</b> 7     |

|         | 2-10 X and Y Driveline Logic                     | 2 <del>-</del> 8 |

|         | 2-11 Memory Core Sensing and Preamp Logic        | 2-9              |

|         | 2-12 BMU Ancillary Logic                         | 2-9              |

|         | 2-13 Airflow and Voltage Monitor Circuits        | 2-10             |

|         | 2-14 Timing Pulse Protection Circuits            | 2-10             |

|         | 2-15 Predrive Disable Circuit                    | 2-11             |

|         | 2-16 Voltage Generation and Regulation Circuits  | 2-11             |

|         | 2-17 Preamp Select and Strobe Driver Circuits    | 2-11             |

| III     | DETAIL PRINCIPLES OF OPERATION                   | 3-1              |

|         | 3-1 Introduction                                 | 3-1              |

|         | 3-2 Sigma 3 Power Distribution                   | 3-2              |

|         | 3-3 Memory Protect Features                      | 3 <del>-</del> 5 |

|         | 3-4 Power Monitor System                         | 3-7              |

# TABLE OF CONTENTS (Cont.)

| Section |                   | Title                                                     | Page              |

|---------|-------------------|-----------------------------------------------------------|-------------------|

|         | 3 <b>-</b> 5      | PT17B Shutdown                                            | 3-9               |

|         | 3-6               | Sigma 3 Core Memory Logic                                 | 3 <b>-</b> 9      |

|         | 3-7               | Signal Distribution                                       | 3-10              |

|         | <b>3-8</b>        | Memory Port Multiple (MPM) - Assembly No. 149395          | 3-12              |

|         | 3-9               | Address Decode (Port Address-Here) Logic                  | 3-15              |

|         | 3 <del>-</del> 10 | Reset-Early Logic                                         | 3-19              |

|         | 3 <b>-</b> 11     | MPM Timing and Control Logic                              | 3-22              |

|         | 3 <del>-</del> 12 | Port Selection and Memory Address Register Logic          | 3-26              |

|         | 3 <del>-</del> 13 | APRIORITY-NORMAL True                                     | 3-26              |

|         | 3-14              | APRIORITY-NORMAL False                                    | 3-30              |

|         | 3 <b>-</b> 15     | Memory Address Register Logic                             | 3-31              |

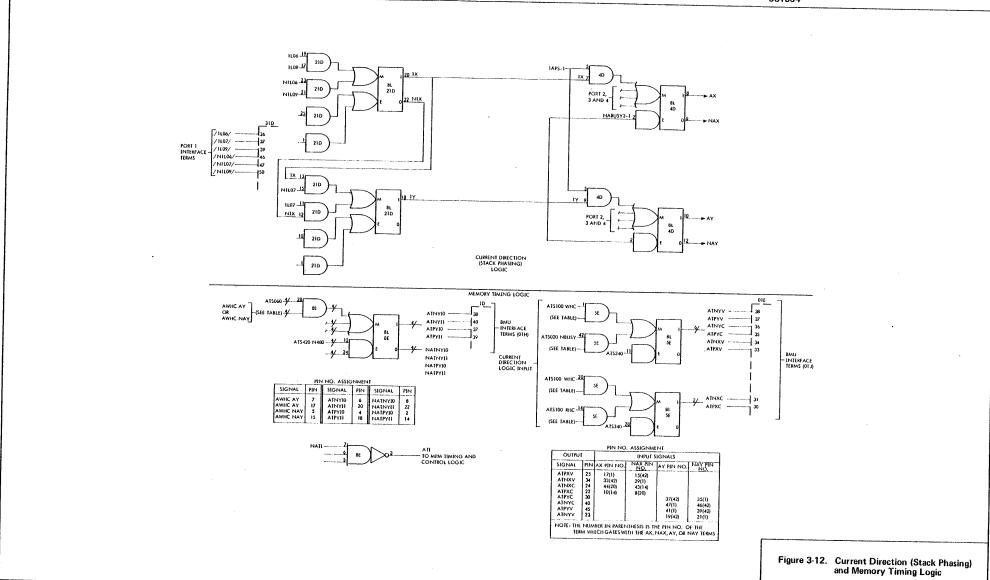

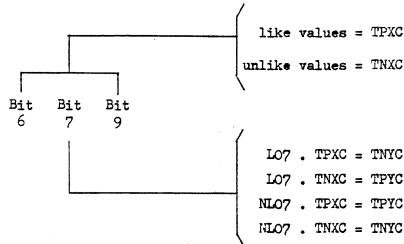

|         | 3 <del>-</del> 16 | Stack Phasing (Current Direction) and Timing Logic        | 3-33              |

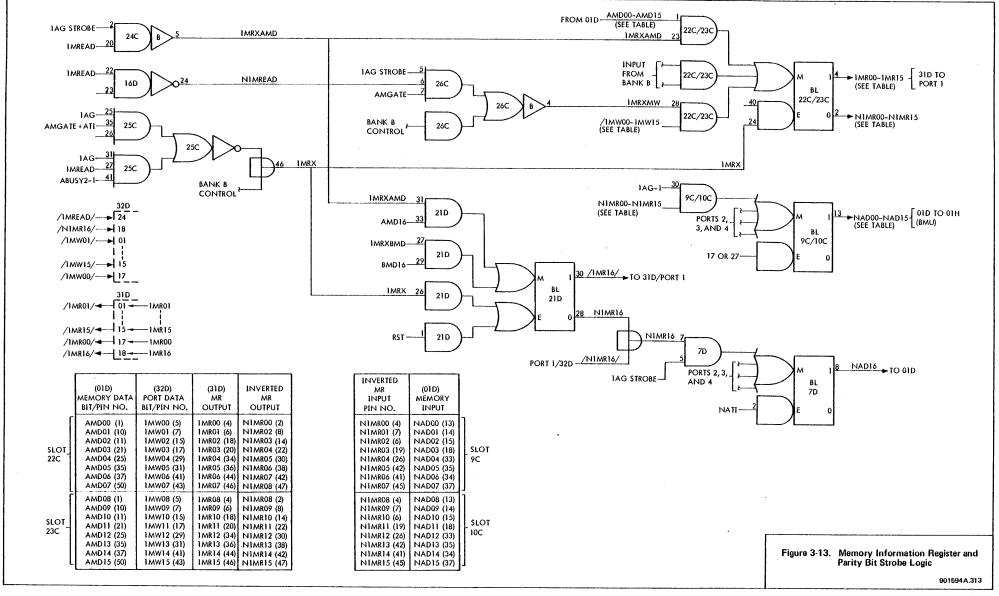

|         | 3 <del>-</del> 17 | Memory Information Register Logic                         | 3-37              |

|         | 3-18              | Parity Bit Strobe Logic                                   | 3-39              |

|         |                   | Basic Memory Unit (BMU) - Assembly No. 148418             | 3-40              |

|         | 3-19<br>3-20      | Core Diode Modules FFT13 and FFT14                        | 3-40              |

|         | _                 | Magnetic Core                                             | 3-43              |

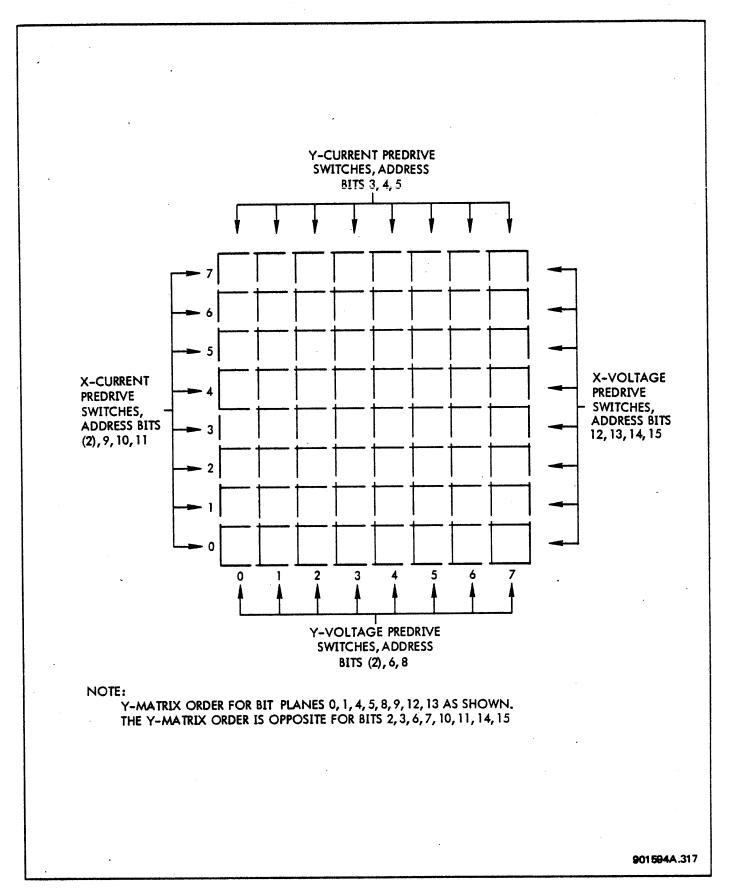

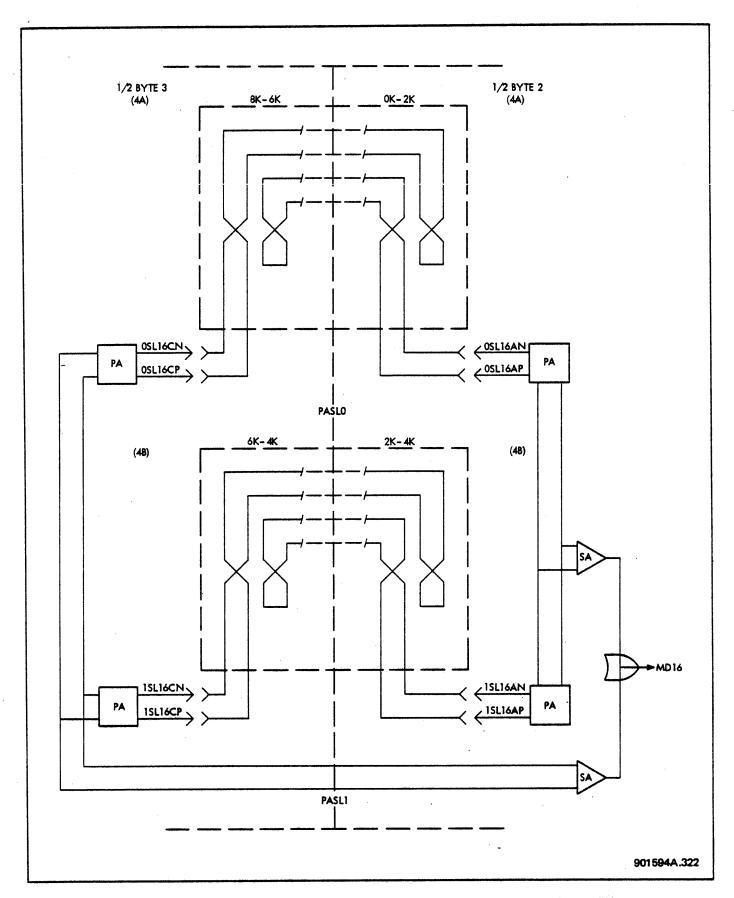

|         | 3-21              | X and Y-Driveline and Y-Inhibit Logic                     | 3-48              |

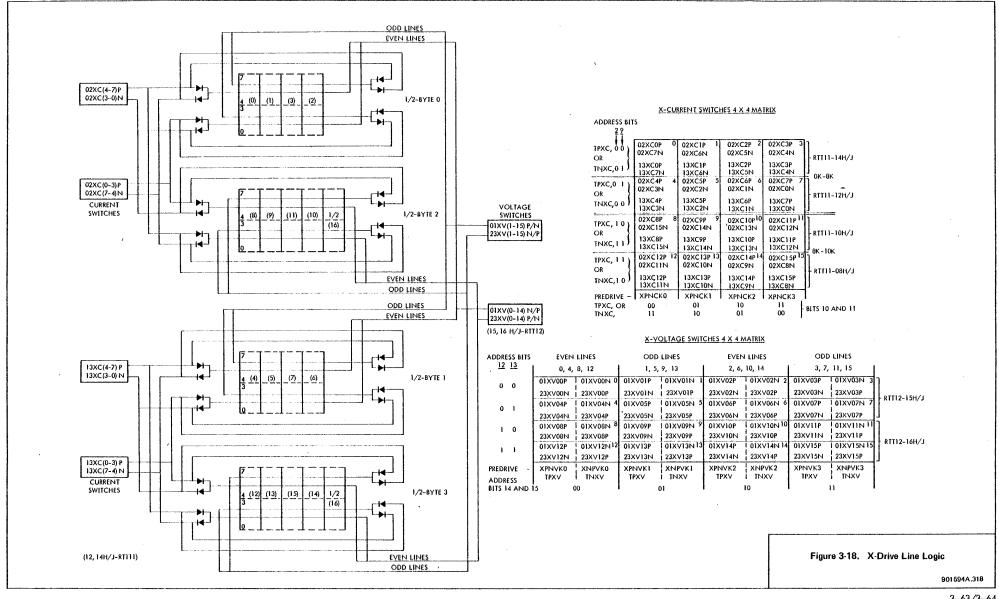

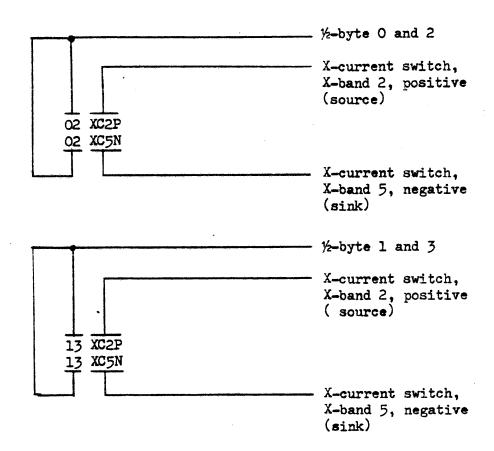

|         | <b>3-22</b>       | X-Driveline Circuits - Modules RTT11 and RTT12            | 3-51              |

|         | 3 <del>-</del> 23 | X-Band Selection                                          | 3-52              |

|         | <b>3-</b> 24      | X-Line Selection                                          | 3-54              |

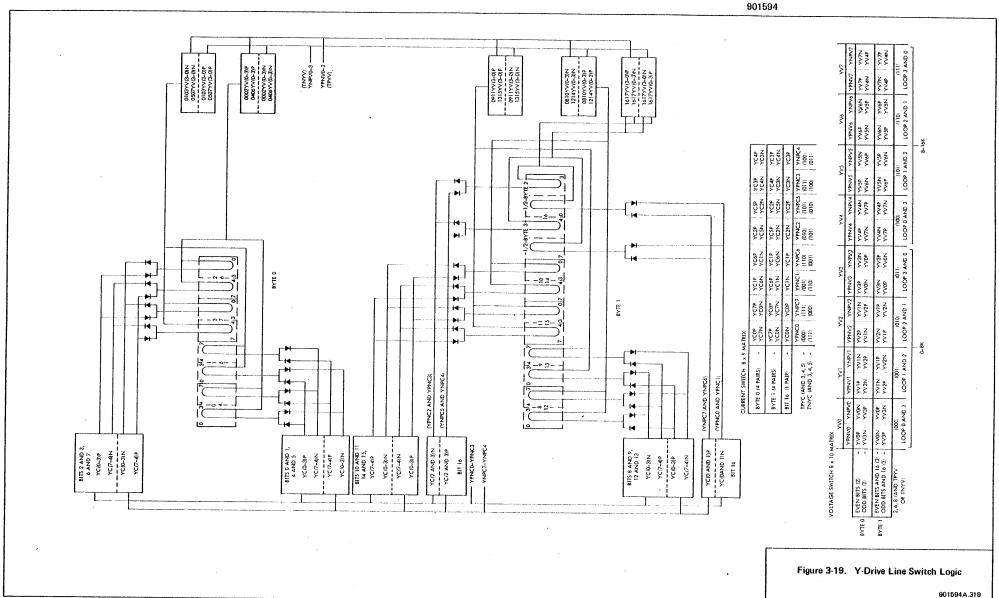

|         | 3 <b>-</b> 25     | Y-Driveline Circuits - Modules RTT10 and RTT11            | 3-56              |

|         | 3-26              |                                                           | 3-59              |

|         | 3-27              | Y-Column Selection                                        | 3-60              |

|         | 3-28              | X-Line Loop Selection                                     | <i>)</i>          |

|         | 3-29              | Y-Driveline Inhibit Circuits - Modules RTT11<br>and RTT12 | 3-64              |

|         | 3-30              | X and Y-Driveline Coincidence                             | 3-65              |

|         | 3-31              | Core Sensing and Preamp Logic - Module HTT10              | 3-66              |

|         | 3-32              | Parity Bit-Plane Sense Line Pattern and Channel           | 3-69              |

|         | 3-33              | BMU Ancillary Logic - Module WTT10                        | 3-69              |

|         | 3-34              | Sense Amplifier Support Logic                             | 3-69              |

|         | 3-35              | Preamp Select Circuit                                     | 3-71              |

|         | 3-36              | Strobe Driver Circuit                                     | 3-71              |

|         | 3-37              | V. Generator/Regulator                                    | 3-71              |

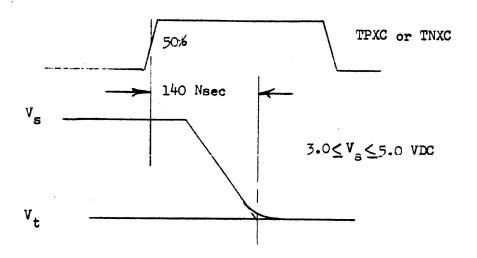

|         | 3-38              | Vs Regulator                                              | 3 <del>-</del> 72 |

|         | 3-39              | V <sub>t</sub> Regulator                                  | 3 <del>-</del> 72 |

|         | 3-40              | VM Regulator                                              | 3-72              |

|         | 3-41              | Memory Protect Circuits                                   | 3 <del>-</del> 72 |

|         | 3-42              | Predrive Disable Circuit                                  | 3-73              |

|         | 3-43              | Airflow Monitor Circuit                                   | 3-73              |

|         | 3-44              | Voltage Monitor Circuit                                   | 3-74              |

|         | 3-45              | MSTAT                                                     | 3-74              |

|         | 7 1.6             | Minima Balan Protection Circuit                           | 3-74              |

# TABLE OF CONTENTS (Cont.)

| Section | Title                                                                | Page                     |

|---------|----------------------------------------------------------------------|--------------------------|

| IV      | INSTALLATION AND VERIFICATION                                        | 4-1                      |

|         | 4-1 Introduction                                                     | 4-1                      |

|         | 4-2 References                                                       | 4-1                      |

|         | 4-3 Sigma 3 Core Memory Installation                                 | 4-2                      |

|         | 4-4 Memory Frame Assembly 153259                                     | 4-2                      |

|         | 4-5 Bank B Option                                                    | 4-2                      |

|         | 4-6 Basic Memory Unit (EMU) 148418                                   | 4-3                      |

|         | 4-7 Bank B Drive Assembly 149401                                     | 4-3                      |

|         | 4-8 8K to 16K Memory Expansion Kit 149668                            | 4-4                      |

|         | 4-9 Memory Port 2, 3, or 4 Assemblies                                | 4-5                      |

|         | 4-10 Sigma 3 Core Memory Installation Verification                   | 4-5                      |

|         | 4-11 Memory Frame Assembly 153259                                    | 4-6                      |

|         | 4-12 Bank B Option                                                   | 4-6                      |

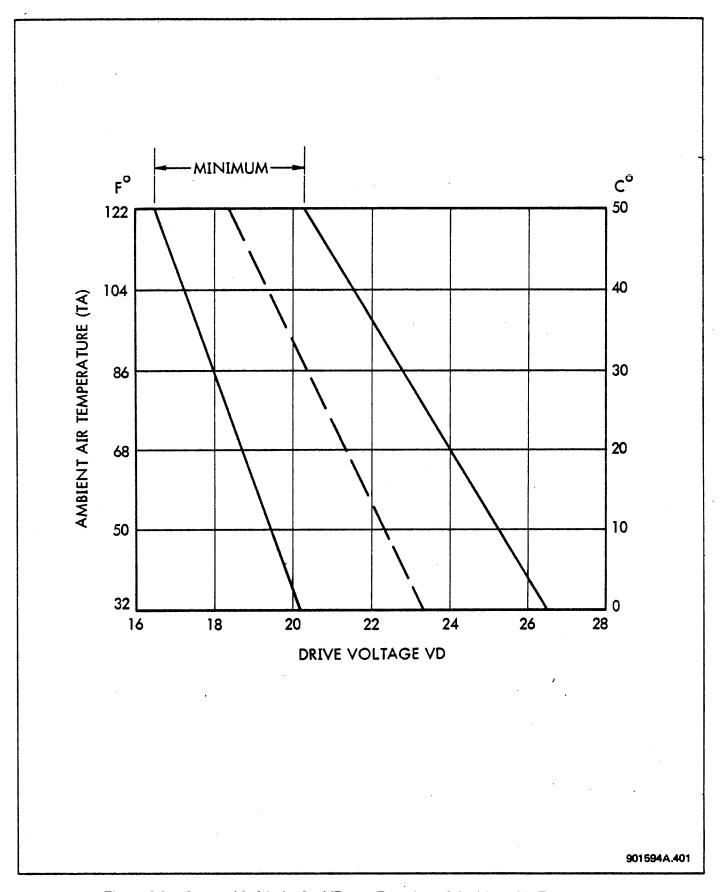

|         | 4-13 Optimum VD Adjustment (Schmooing)                               | 4-9                      |

|         | 4-14 8K to 16K Memory Expansion Kit 149668 Installation Verification | 4-9                      |

| V       | FIELD MAINTENANCE PROCEDURES                                         | 5-1                      |

|         | 5-1 Introduction                                                     | 5-1                      |

|         | 5-2 References                                                       | 5-1                      |

|         | 5-3 Preventive Maintenance                                           | 5 <b>-</b> 2             |

|         | 5-4 Cleaning                                                         | 5 <del>-</del> 3         |

|         | 5-5 Air Filter                                                       | 5-3<br>5-3<br>5-4<br>5-4 |

|         | 5-6 Voltage Verification                                             | 5-4                      |

|         | 5-7 Temperature Sense Shutdown Test                                  | 5-4                      |

|         | 5-8 Memory System Margin Test                                        | 5-5                      |

|         | 5-9 Corrective Maintenance                                           | 5-5                      |

|         | 5-10 Troubleshooting and Repair Procedures                           | 5-5                      |

|         | 5-11 Cleaning Module Contacts                                        | 5-13                     |

|         | 5-12 PT17B Power Supply 148806 Removal                               | 5-13                     |

|         | 5-13 PT17B Power Supply 148806 Replacement                           | 5-13                     |

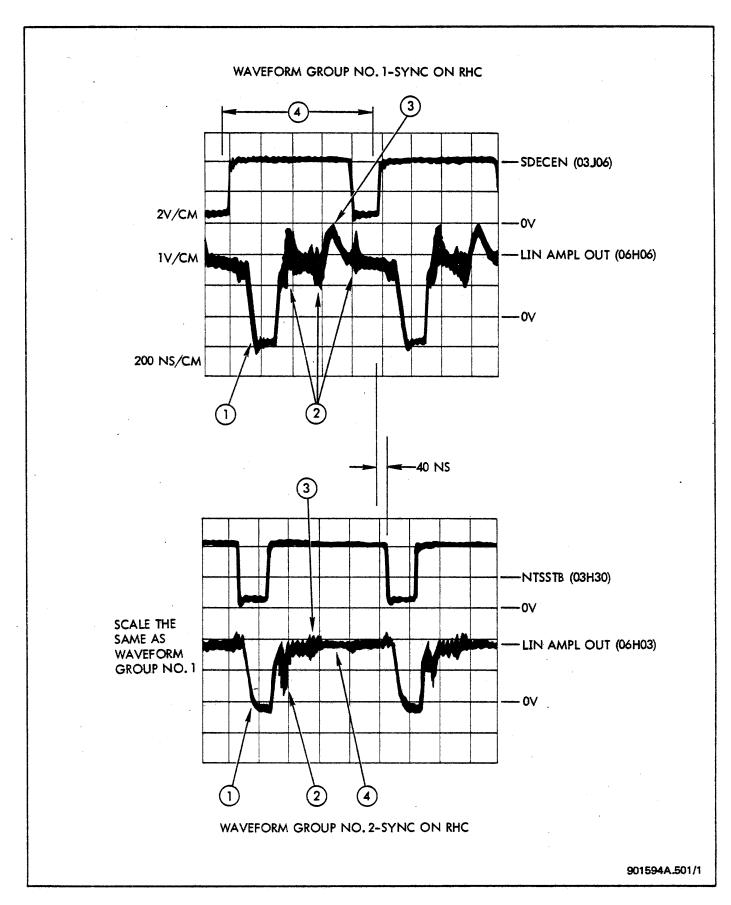

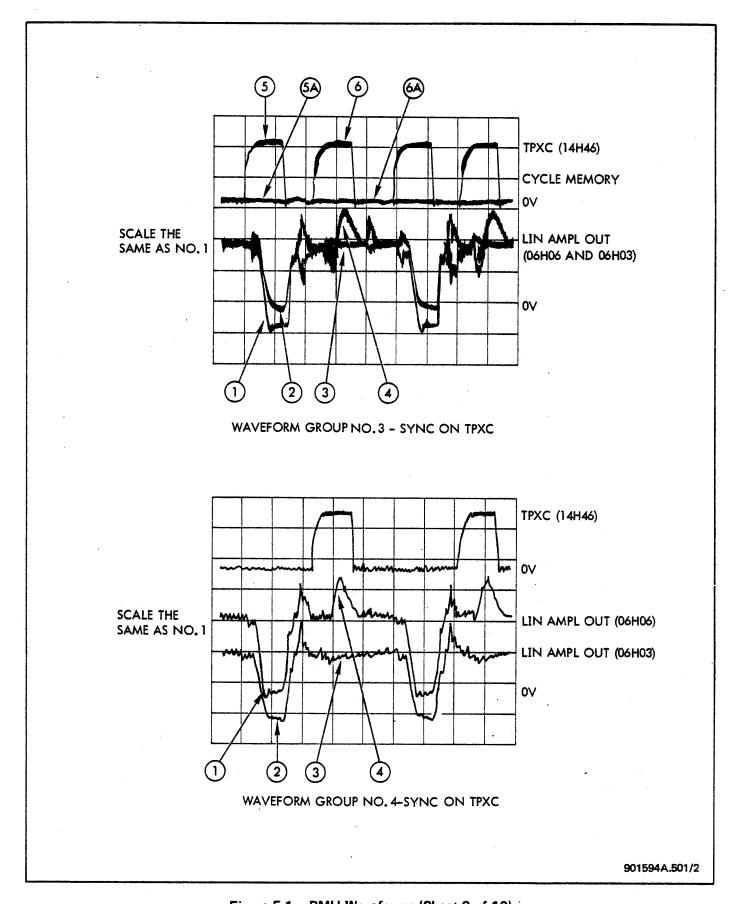

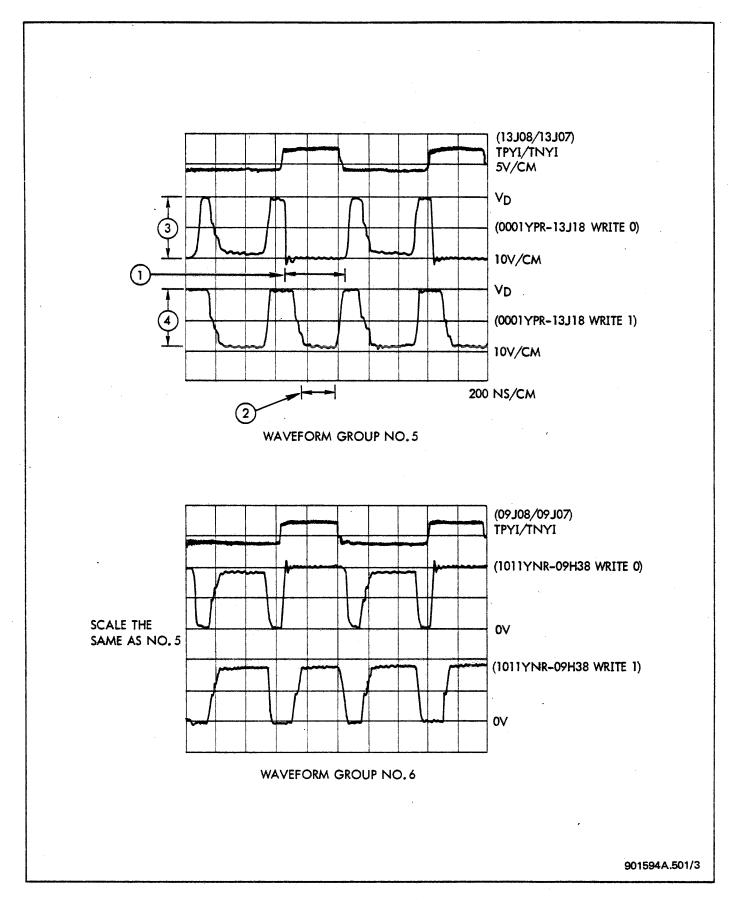

|         | 5-14 Waveforms                                                       | 5-1 <sup>1</sup>         |

| VI      | ILLUSTRATED PARTS BREAKDOWN                                          | 6-1                      |

|         | 6-1 Group Assembly Parts List                                        | 6-1                      |

|         | ( ) Nome and and Tradem                                              | 6_1                      |

# LIST OF ILLUSTRATIONS

| Figure                   | Title                                                      | Page              |

|--------------------------|------------------------------------------------------------|-------------------|

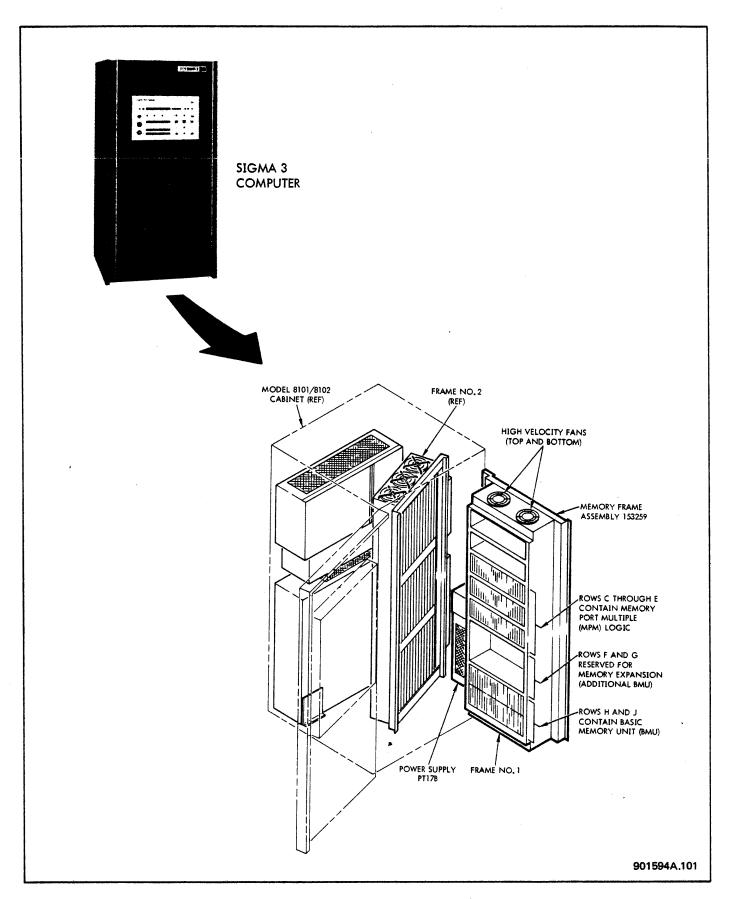

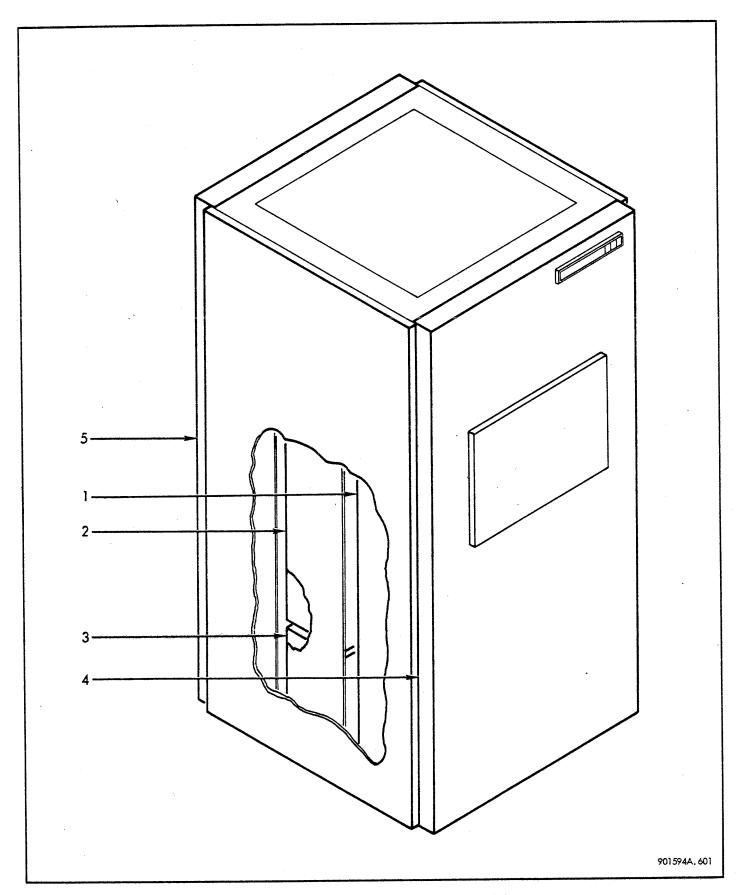

| 1-1                      | Sigma 3 Core Memory Location in 8101/8102 Model Cabinet    | 1-4               |

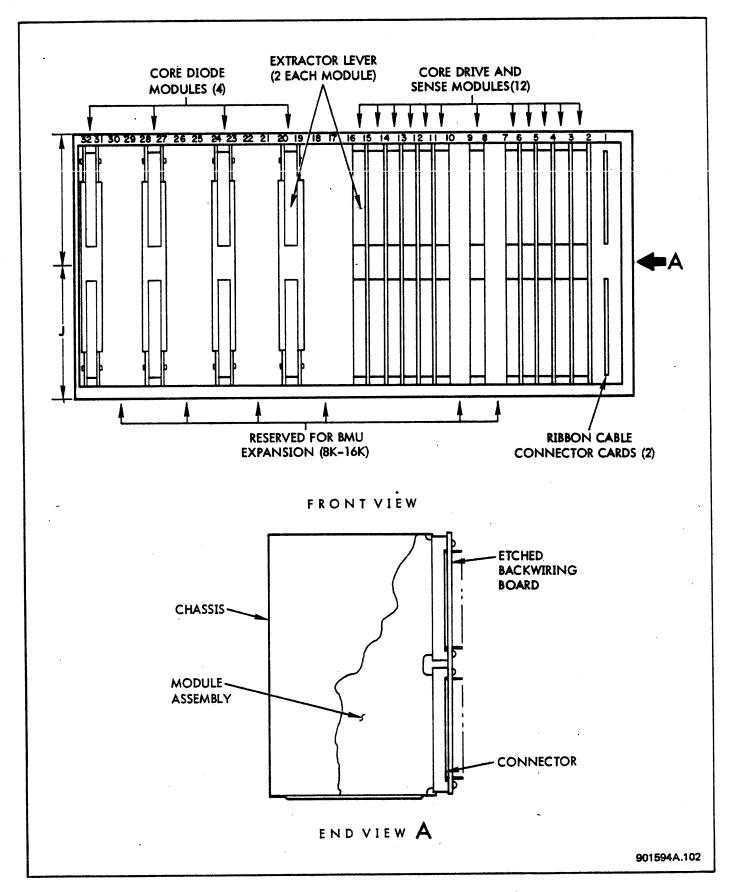

| 1-2                      | BMU Configuration for Basic Memory System                  | 1-6               |

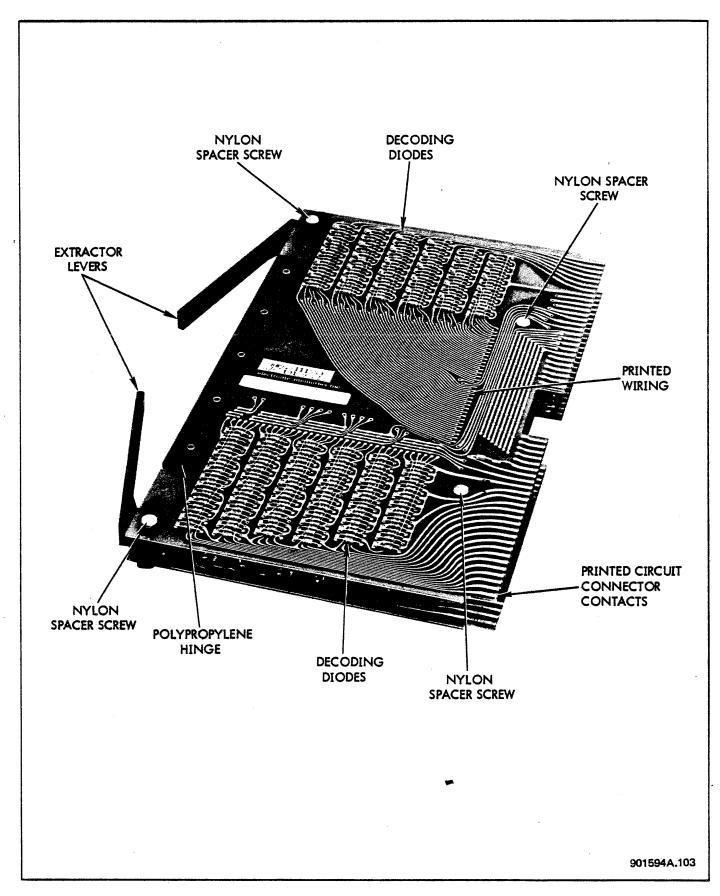

| 1-3                      | Core Diode Module (CDM)                                    | 1-7               |

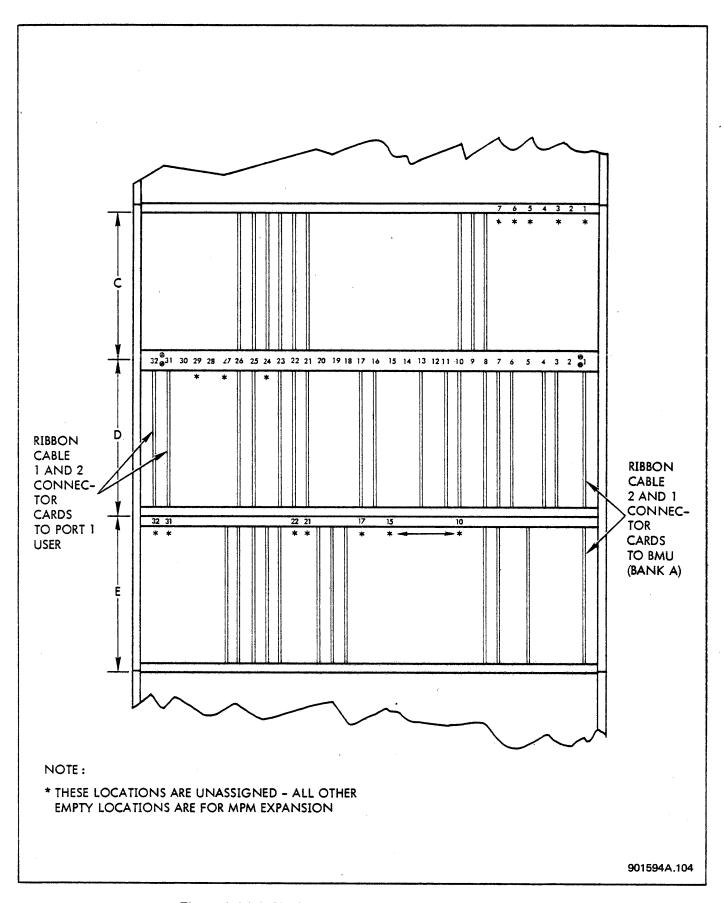

| 1-4                      | MPM Configuration for Basic Memory System                  | 1-9               |

|                          | Relation of the 8K Basic Memory System to Sigma 3 Computer |                   |

| 1-5                      | System of 64K                                              | 1-10              |

| 1-6                      | 8K Basic Memory Frame Assembly and Expansion Capabilities  | 1-13              |

| 2-1                      | Basic Memory System, Functional Flow Block Diagram         | 2-2               |

| 3-1                      | Sigma 3 Power Distribution                                 | 3 <del>-</del> 3  |

|                          | Power Distribution to Sigma 3 Core Memory                  | <b>3–</b> 6       |

| 3 <del>-</del> 2         | Sigma 3 Power Monitor System (Power Fail-Safe) and PT17B   |                   |

| 3 <del>-</del> 3         | Shutdown                                                   | 3 <del>-</del> 8  |

| 3_4                      | Detailed Principles of Operation, Block Diagram            | 3-11              |

|                          | Buffered Latch, 309                                        | 3-14              |

| 3 <del>-</del> 5         | Address Decode and Reset Early Logic                       | 3-17              |

| 3 <b>-</b> 6             | MPM Timing and Control Logic                               | 3 <del>-</del> 21 |

| 3 <del>-</del> 7<br>3-8  | Control Signals Timing Diagram                             | 3 <del>-</del> 23 |

| -                        | Port Select and Memory Address Register Logic              | 3 <del>-</del> 25 |

| 3 <del>-</del> 9<br>3-10 | Port Selection Timing Diagram                              | <b>3–</b> 28      |

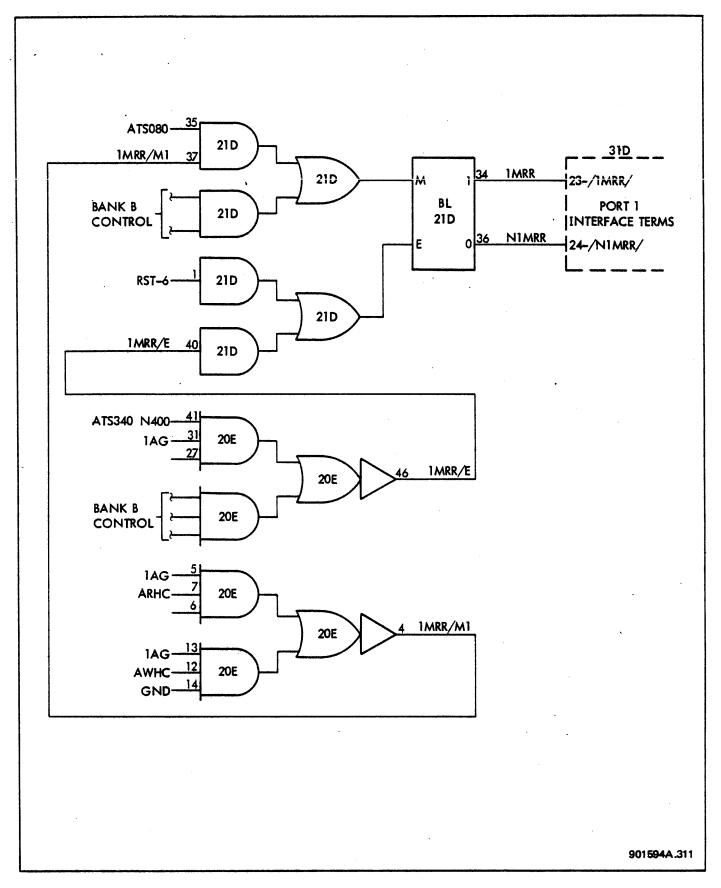

| 3-11                     | Memory Request Release Logic                               | 3 <del>-</del> 29 |

| 3-12                     | Current Direction (Stack Phasing) and Memory Timing Logic  | 3-35              |

| 3-13                     | Memory Information Register and Parity Bit Strobe Logic    | 3 <b>-</b> 38     |

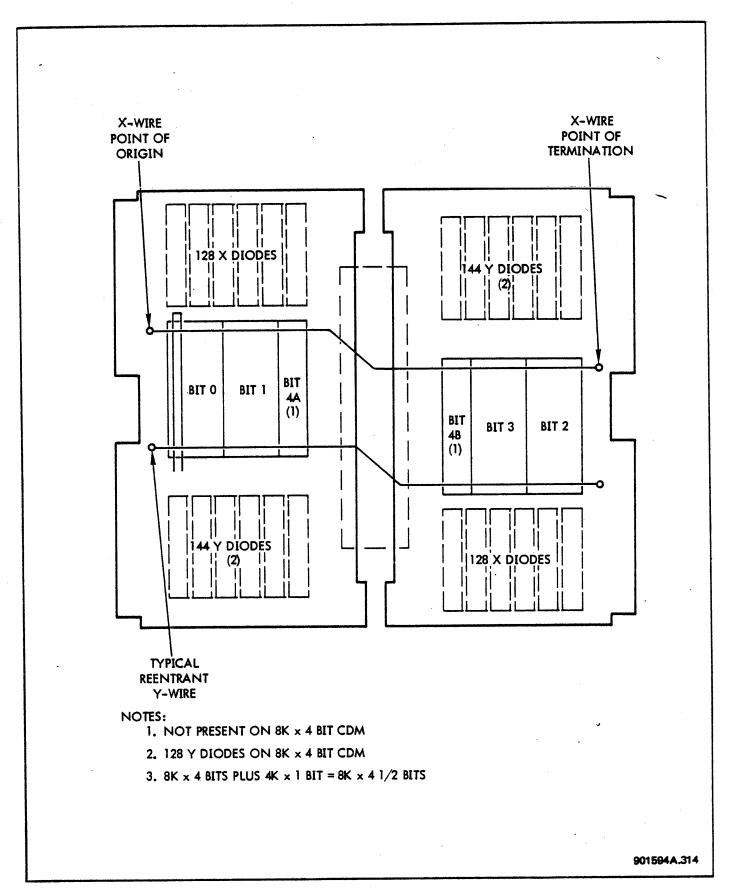

| 3-14                     | 8K x 4 1/2 Bits - Core Diode Module Layout                 | 3-42              |

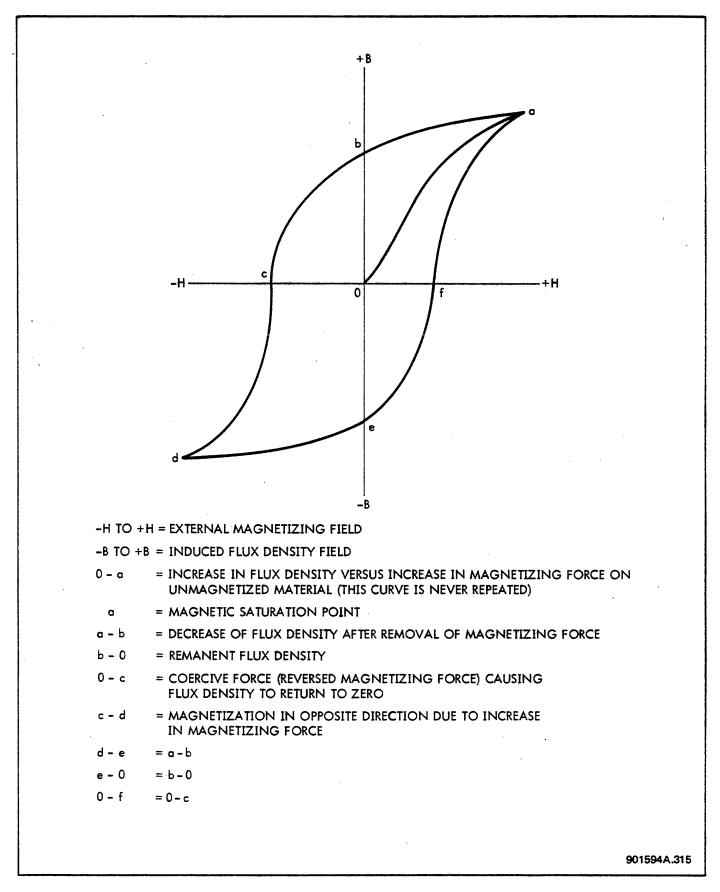

| 3-15                     | Hysteresis Loop (Typical Ferromgnetic Material)            | 3-45              |

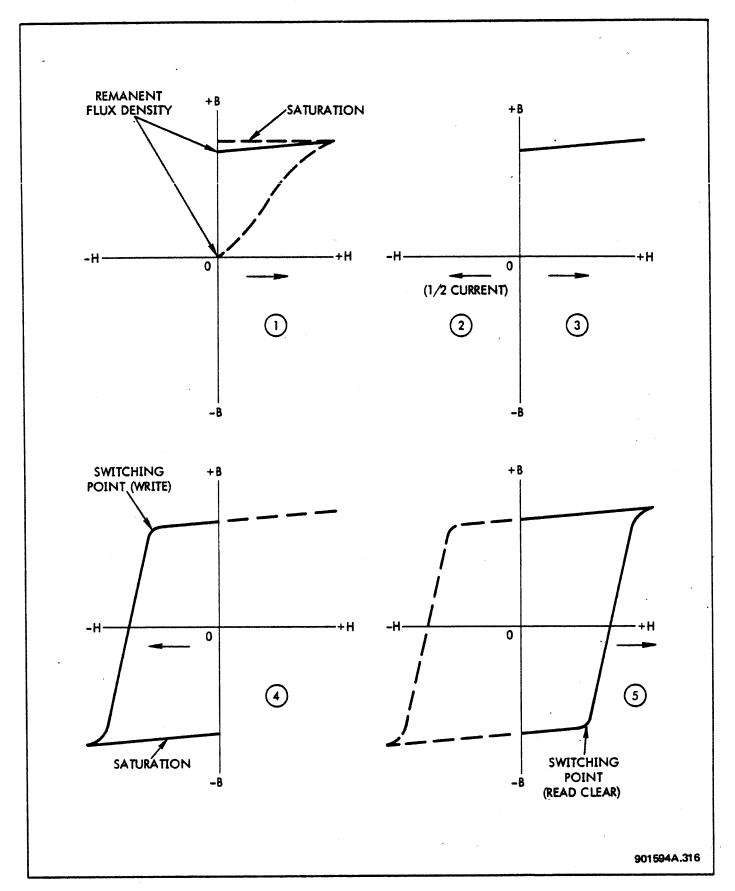

| 3 <b>-</b> 16            | Square Hysteresis Loop - Memory Magnetic Core              | 3-46              |

| 3-17                     | Typical Bit Plane Division for Core Location               | 3 <del>-</del> 50 |

| 3 <b>-1</b> 8            | X-Drive Line Logic                                         | 3-53              |

| 3 <del>-</del> 19        | Y-Driveline Switch Logic                                   | 3 <del>-</del> 58 |

| 3 <del>-</del> 20        | Coincident and Anticoincident Selection and Sense Line     | •                 |

| <del>5-20</del>          | Pattern                                                    | 3-61              |

| 3-21                     | Typical Sense Line Channel for OK-8K - Bit O Shown         | <b>3-</b> 68      |

| 3 <del>-</del> 22        | Sense Line Pattern and Channel for Bit Plane 16 (Parity)   |                   |

| ) <del>-</del> 22        | OK-8K                                                      | 3-70              |

| 4-1                      | Acceptable Limits for VD as a Function of Ambient Air      |                   |

| 4-T                      | Temperature                                                | 4-10              |

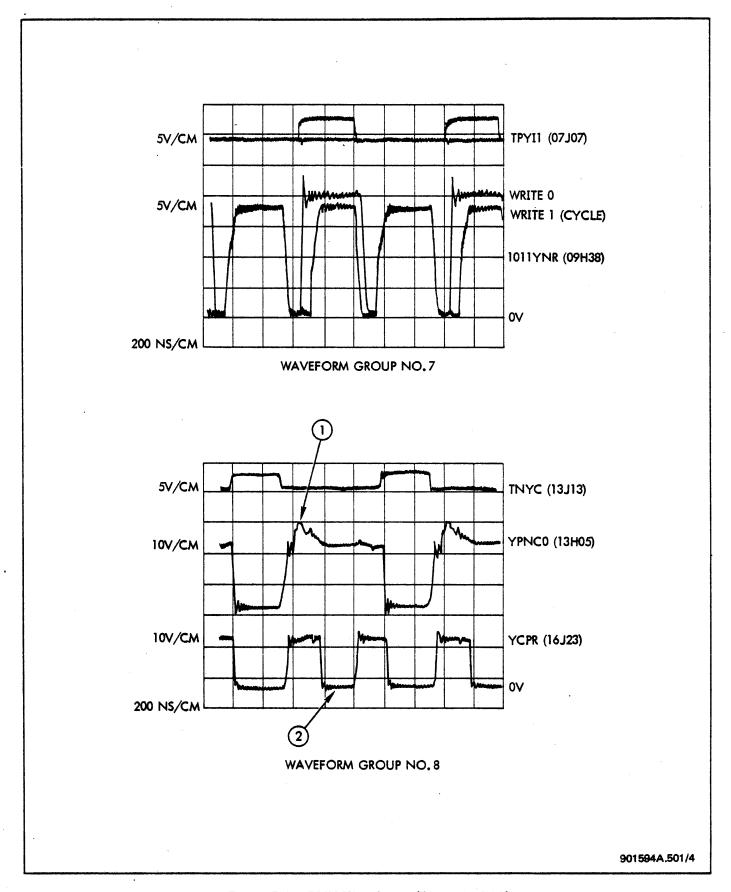

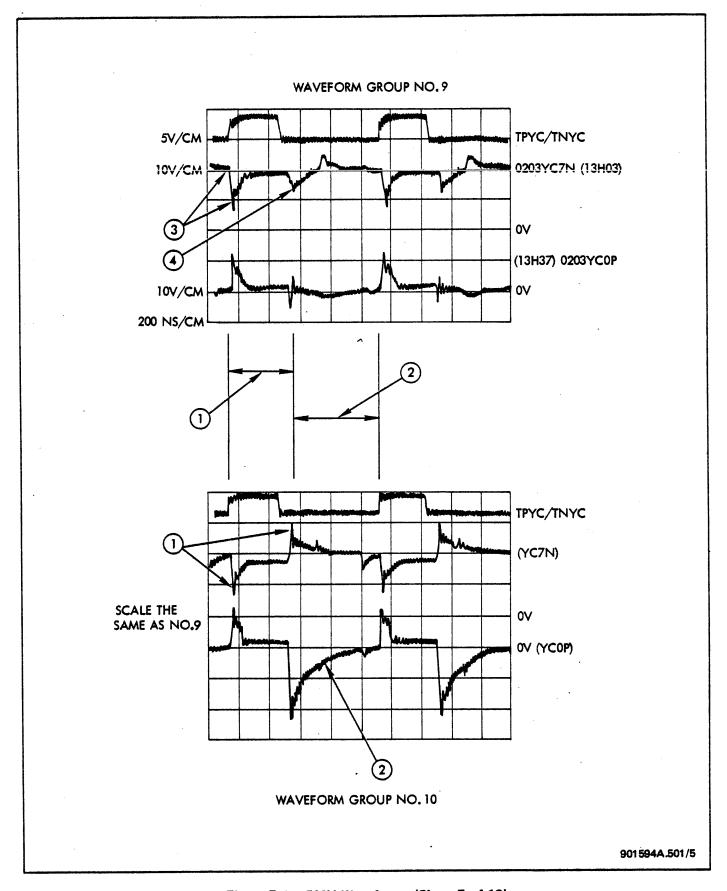

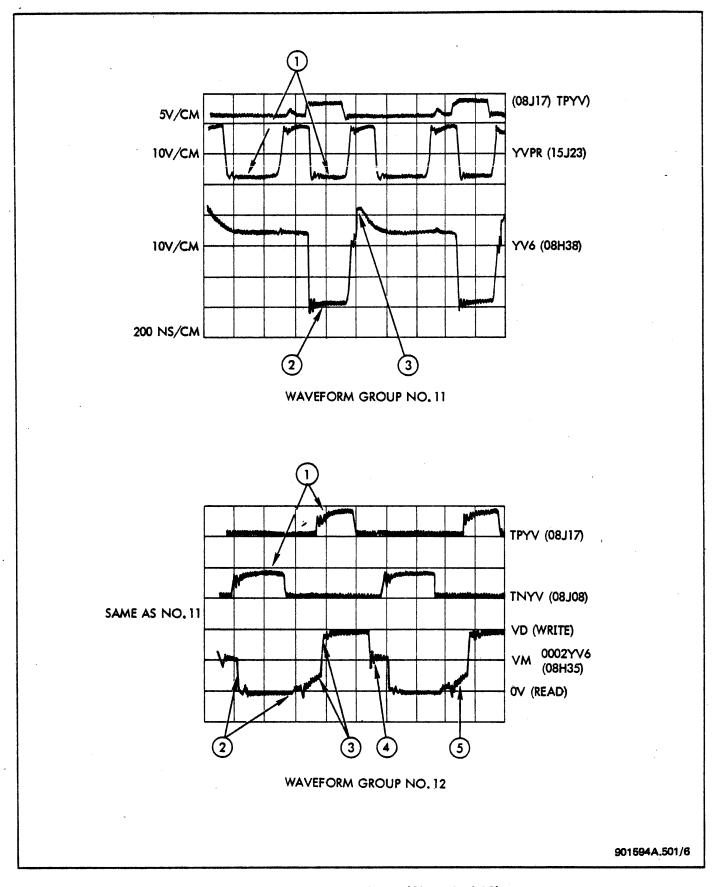

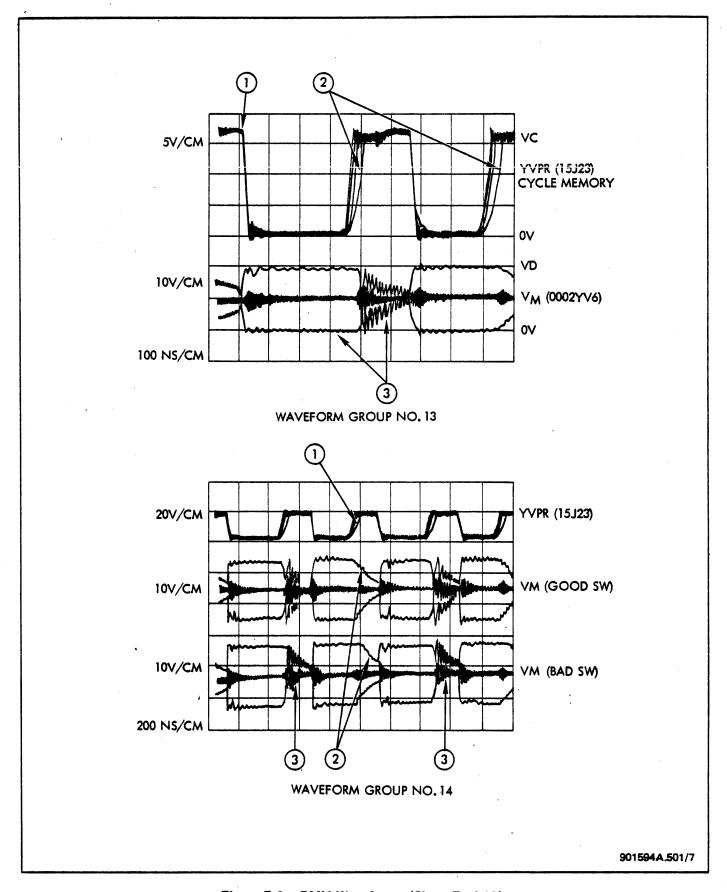

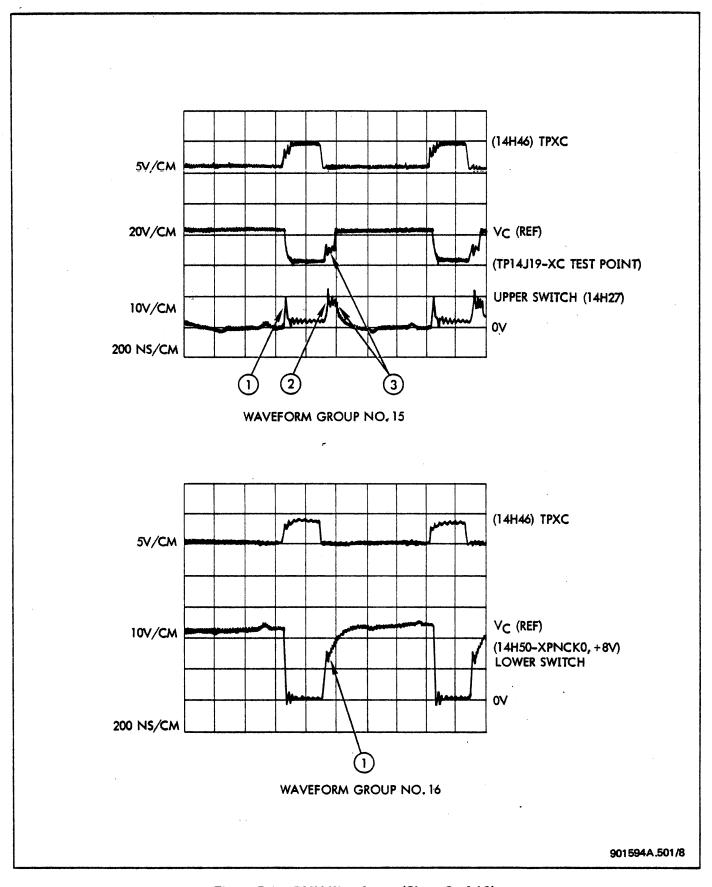

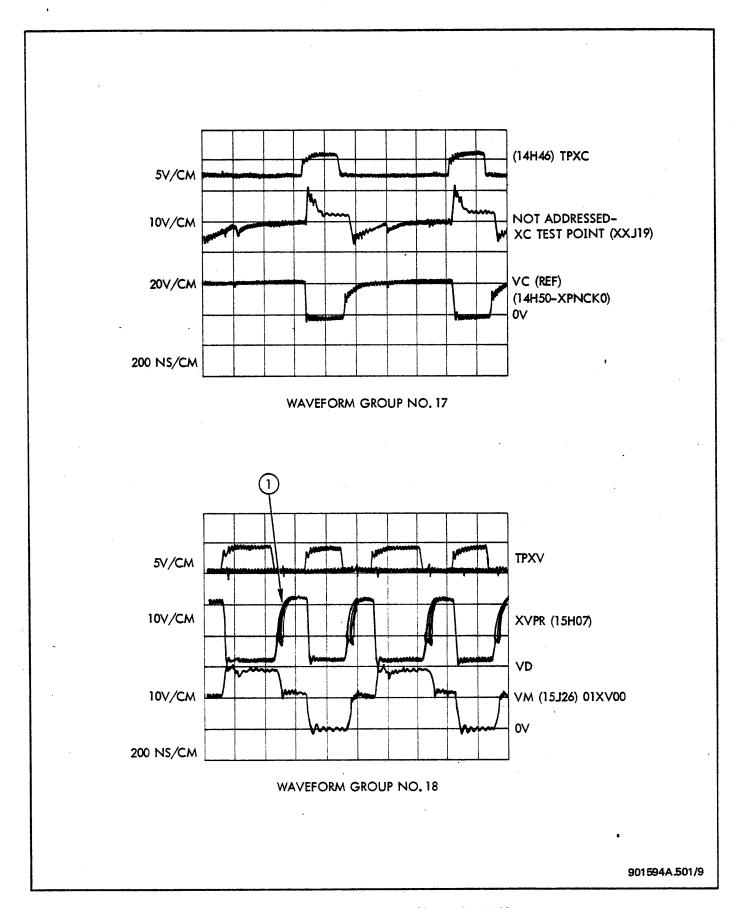

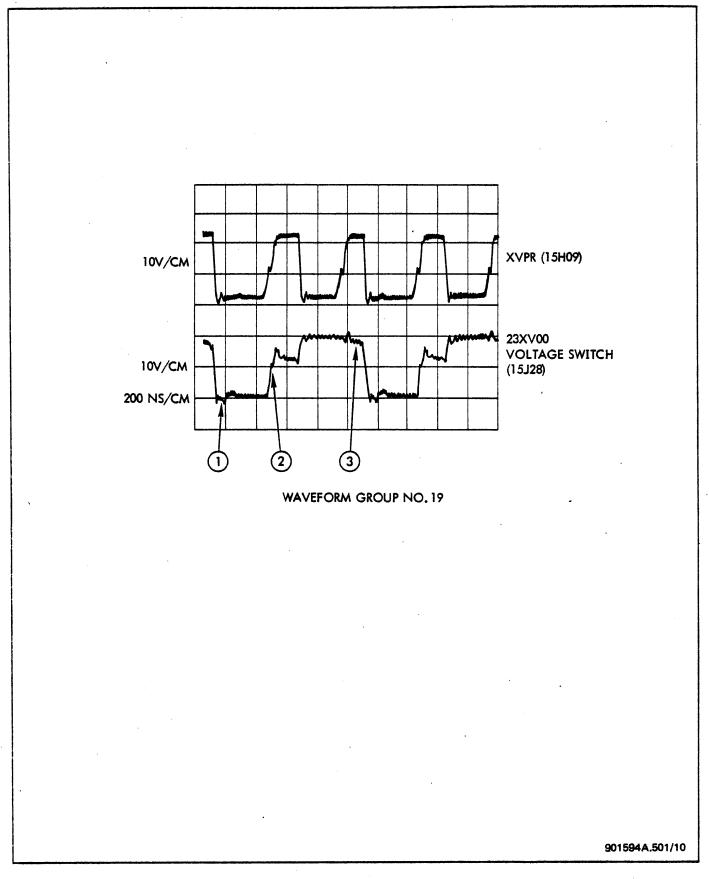

| 5-1                      | HMU Waveforms                                              | 5-15              |

| 6 <b>-</b> 1             | Sigma 3 Core Memory                                        | 6-3               |

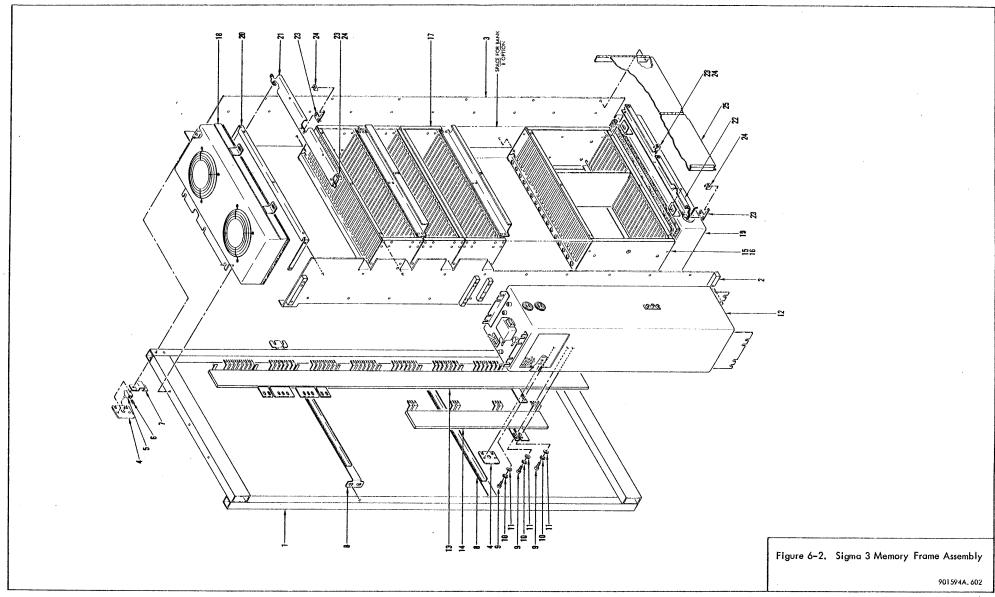

| 6 <del>-</del> 2         | Sigma 3 Memory Frame Assembly                              | 6-5               |

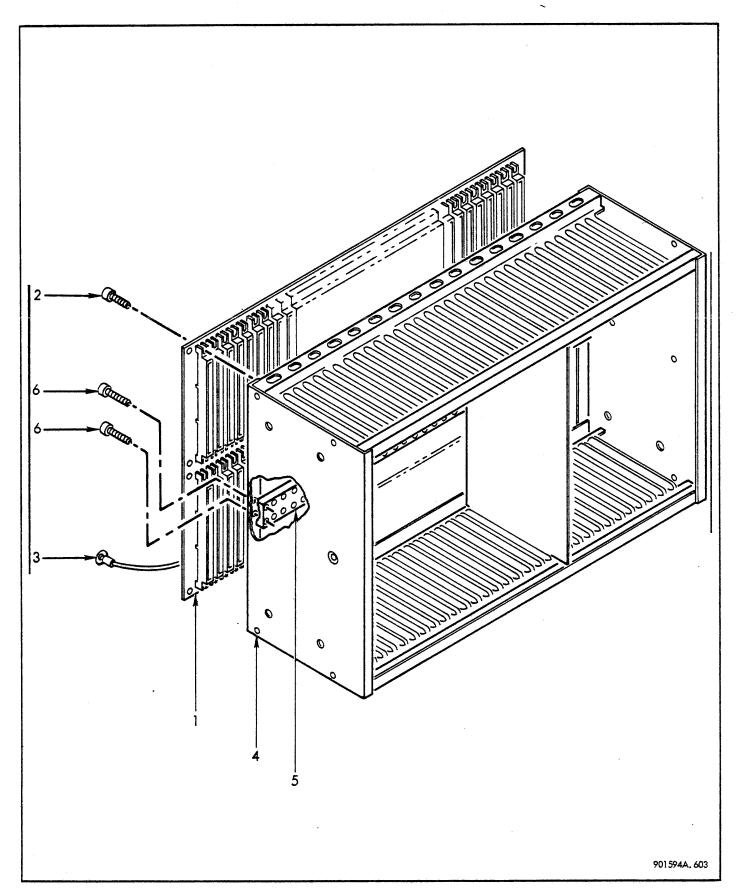

| 6 <b>-</b> 3             | 8K Basic Memory Assemblies                                 | 6-10              |

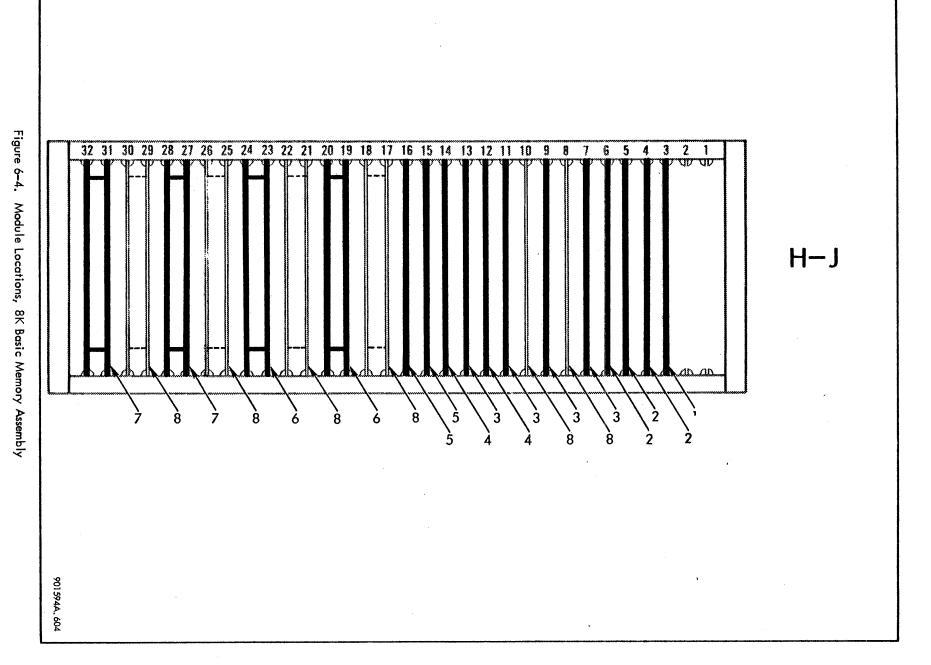

| 6 <b>-</b> 4             | Module Locations, 8K Basic Memory Assembly                 | 6-12              |

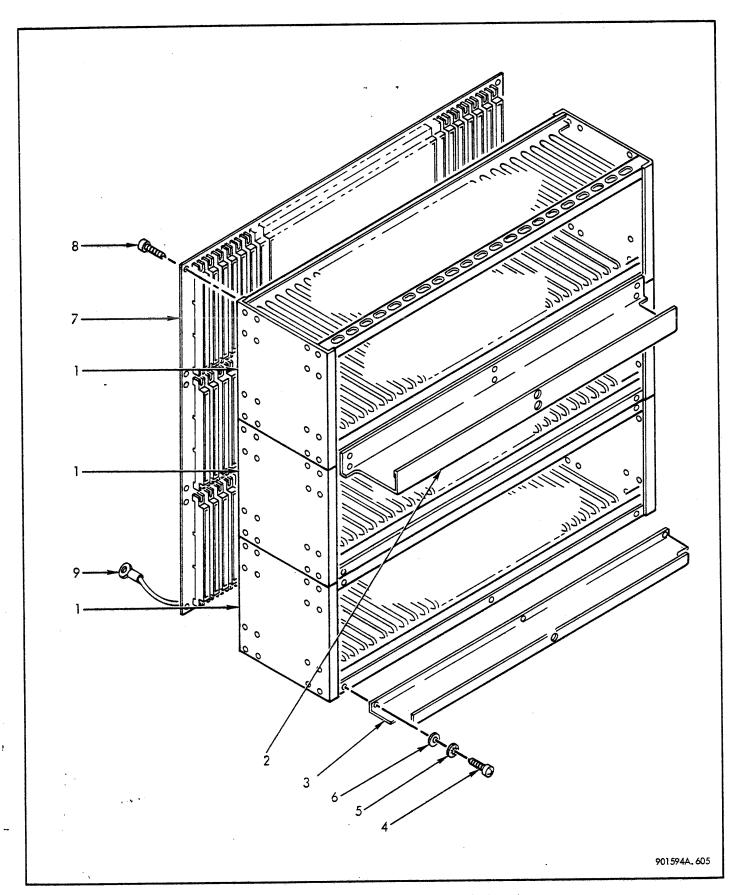

| 6-5                      | Memory Port Multiple Assemblies (MPM)                      | 6-14              |

| 6 <b>-</b> 6             | Module Locations, MPM Assembly                             | 6-16              |

| 6 <del>-</del> 7         | Module Locations, Bank B Drive and Port Assemblies         | 6-18              |

## LIST OF TABLES

| Table            | Title                                                      | Page     |

|------------------|------------------------------------------------------------|----------|

| 3-1              | Port Address-Here Switch Designations and Locations        | 3-16     |

| 3 <del>-</del> 2 | Port Address-Here Decoding                                 | 3-16     |

| 4-1              | Maintenance and Support Documentation                      | 4-1      |

| 4-2              | Test Equipment, Special Tools and Materials Required       | 4-2      |

| 5 <del>-</del> 1 | Maintenance Support Documents, Special Tools and Materials | 5-1      |

| 5 <del>-</del> 2 | Preventive Maintenance Procedures                          | 5-2      |

| 5 <del>-</del> 3 | Troubleshooting and Repair Procedures                      | 5-7      |

| 6-1              | Sigma 3 Core Memory                                        | 6-4      |

| 6-2              | Sigma 3 Memory-Frame Assembly                              | 6-6      |

| 6-3              | 8K Basic Memory Assembly                                   | 6-11     |

| 6 <del>-</del> 4 | Module Locations, 8K Basic Memory Assembly                 | 6-13     |

| 6 <del>-</del> 5 | Memory Port Multiple Assembly (MPM)                        | 6-15     |

| 6 <b>-</b> 6     | Module Locations, MPM Assembly                             | 6-17     |

|                  | Module Locations, Bank B Drive and Port Assemblies         | 6-19     |

| 6-7              | WOUNTE TOCKTIOUR DEUK D DEIAG SUG LOLL VOSEMETTED          | <u> </u> |

# LIST OF RELATED PUBLICATIONS

| <u>Title</u>                                                                                 | Publication<br>Number |

|----------------------------------------------------------------------------------------------|-----------------------|

| Sigma Computer Systems Interface Design Manual                                               | 900973                |

| Sigma 3 Memory Diagnostic, MEDIC 2/3, No. 704022,                                            |                       |

| Diagnostic Programming Manual                                                                | 900676                |

| Sigma 3 Computer Reference Manual                                                            | 901592                |

| Sigma 3 Central Processor, Model 8101, Technical Manual                                      | 901593                |

| Sigma 3 External Input/Output Processor, Model 8171, Assembly No. 148557, Technical Manual   | 901595                |

| Sigma 3 Memory Diagnostic - Fault Locator, Technical Manual                                  | 901604                |

| Sigma 3 Multiport Random Exercisor, Program No. 705672, Diagnostic Programming Manual        | 901615                |

| Power Supply, Model PT14B, Assembly No. 148803, Power Supply Data Package                    | 901655                |

| Power Supply, Model PT15B, Assembly No. 148804, Power Supply Data Package                    | 901656                |

| Power Supply, Model PT16B, Assembly No. 148805, Power Supply Data Package                    | 901657                |

| Power Supply, Model PT17B, Assembly No. 148806, Power Supply Data Package                    | 901658                |

| Sigma 3 Central Processing Unit, Model 8101, Assembly No. 153253, Engineering Support Manual | 902400                |

| Sigma 3 Core Memory, Model 8151/8152/8155, Assembly No. Engineering Support Manual           | 902401                |

| Sigma 3 External Input/Output Processor, Model 8171,                                         |                       |

| Assembly No. 148557, Engineering Support Manual                                              | 902402                |

### SECTION I

### INTRODUCTION

### 1-1. SCOPE OF MANUAL

This manual contains technical information pertinent to the Sigma 3 Core

Memory which is one of the main units included as part of the Sigma 3

Computer system. This manual describes the Sigma 3 Core Memory both

physically and functionally as applied in the Sigma 3 Computer system.

This manual also includes information necessary to install and maintain the memory unit in the field of operation.

### 1-2. CONTENT OF MANUAL

The contents of this manual are sectionalized as follows: Section I contains an introduction to the equipment covered by the manual and to the method and type of coverage.

Section II contains a general description of the basic memory system operation. The overall mode of operation is divided into several functional groups of logic and each group is analyzed in the order of data transfer to, within, and from the memory system.

Section III provides detailed descriptions of the logic elements which comprise each functional group outlined in Section II.

Section IV provides unit installation and checkout procedures.

Section V contains preventive and corrective maintenance precedures for the equipment in the field of operation.

Section VI provides an illustrated parts breakdown and parts list of those field replaceable items and also provides a list of option items for basic memory system expansion.

# 1-3. RELATED PUBLICATIONS

A list of related publications, page , preceding Section I, is provided as additional reference material essential to the maintenance personnel to insure a complete awareness of proper installation, operation and maintenance of the memory system relative to the Sigma 3 Computer system.

# 1-4. PREREQUISITES TO MANUAL USE

In the construction of this manual, it is assumed the user is familiar with the functions of transistorized digital circuitry and can interpret MIL-STD-806B logic symbology. It is also assumed the user can interpret logic functions expressed in logic equation form and is familiar with machine language programming.

It is essential the user is capable of using standard test equipment in diagnosing and repairing hardware malfunction associated with digital equipment and has experience in the operation and treableshooting of magnetic core memories.

### 1-5. SIGMA 3 CORE MEMORY

### 1-6. PHYSICAL DESCRIPTION

The Sigma 3 Core Memory consists of a basic building block of memory with provisions for optional expansion. This basic memory system is physically located in the No. 1 frame position of the Sigma 3 Computer system (Models 8191/8192) cabinet, as shown in figure 1-1.

The basic memory frame assembly consists of a nine-high frame and chassis which contain the logic for a single port access to a starter 8K expandable memory. The frame assembly also provides for the insertion of additional modules for optional memory expansion to a maximum 32K capacity.

The basic memory system occupies five chassis locations; C, D, E, H, and J. Chassis A and B are reserved for system logic other than the memory system, and chassis F and G are reserved for basic memory system expansion. Power supply PT16B, mounted on frame No. 2 provides regulated dc operating voltages of +4.0. -8.0 and +8.0 for logic circuits, and PT17B, mounted on frame No. 1, provides +25 volts (adjustable and non-adjustable) to drive the memory cores. High velocity fans at the top and bottom of the frame provide cooling for the drive circuitry and to keep the core diode modules at a temperature approaching the ambient air. The fans operate from 120V, 60 Hz power.

The basic memory system is physically and functionally divided into two sections; the basic memory unit (BMU) which provides an 8K stack of core and core drive logic, and memory port multiple (MPM) which provides a multiple port memory control with a single port interface.

Figure 1-1. Sigma 3 Core Memory Location in 8101/8102 Model Cabinet

# 1-7. Basic Memory Unit (BMU)

Chassis H and J provide for a fully expanded BMU or 16K of core and core drive logic. The basic memory system, however, contains a BMU consisting of four core diode modules (8K), twelve modules of core drive and sense logic and two ribbon cable connector cards for signal connection to the MPM. Refer to figure 1-2.

Extractor levers on all modules provide easy extraction of the module from the associated connector. Each module assembly terminates in printed circuit connector contacts which mate with spring type contacts in the associated connector mounted on an etched backwiring board (motherboard) at the rear of the chassis.

- 1-8. Core Diode Module (CDM). Each core diode module (figure 1-3) consists of hinged printed boards (2) with magnetic core arrays and associated decoding diodes; the printed circuit boards are insulated from each other by nylon spacers. The CDM is completely symmetrical both physically and electrically which provides for proper operation when inserted in either possible direction.

- 1-9. Core Drive and Sense Logic. The modules which contain the core drive and sense logic (refer to figure 1-2) are single 2-Hi printed circuit boards with board mounted detail electronic parts. These modules are not reversable (for insertion) as the CDMS, however, the modules conform to the general description in paragraph 1-7.

Figure 1-2. BMU Configuration for Basic Memory System

Figure 1-3. Core Diode Module (CDM)

# 1-10. Memory Port Multiple (MPM)

Chassis C, D, and E provide for a fully expanded MPM (four-port access to two expanded BMUS) However, the MPM portion of the basic memory system provides the logic for multiple port control and one port to access one expanded BMU (16K), this configuration is shown in figure 1-4.

The MPM section of the basic memory system consists of 35, one-chassis high modules and the necessary ribbon cable connector cards for connections between one port and the BMU and one port and the user. Each module is a printed circuit board with board mounted detail electronic parts. The modules terminate in printed circuit connector contacts and mate with spring-type contacts in the appropriate connector mounted on an etched backwiring board (motherboard) at the rear of the chassis. Provisions for electrical connections are identical to the basic memory unit, figure 1-2, view A, with the exceptions allowed for single-chassis high modules.

### 1-11. CAPABILITIES

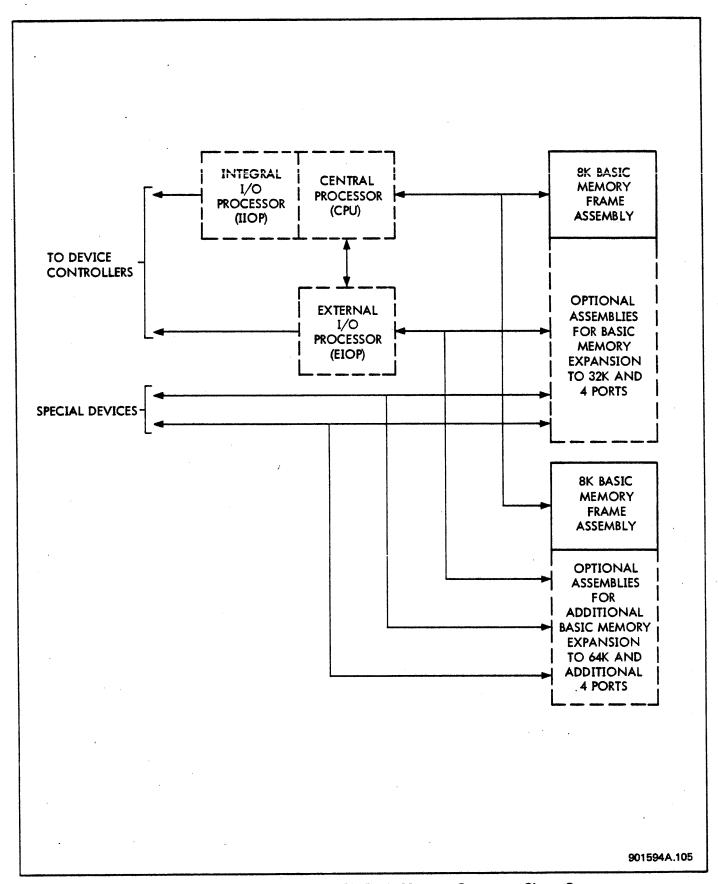

The basic memory frame assembly provides the basic building block of the Sigma 3 Core Memory system. Figure 1-5 is a simplified block diagram showing the relation of this building block to a Sigma 3 Computer system when all optional memory expansion capabilities are utilized.

The basic memory frame assembly provides an 8K stack of core (8196 words) and one memory access port to a central processor (CPU) with an integral I/O processor (IIOP). With the addition of optional module kits, the basic memory can be expanded to provide for an access to a storage capacity of 32,768 words.

Figure 1-4. MPM Configuration for Basic Memory System

Figure 1-5. Relation of the 8K Basic Memory System to Sigma 3 Computer System of 64K

Further port expansion provides for direct communication with special devices selected to use the Sigma 3 Core Memory, and direct communication with an external I/O processor (EIOP) which greatly increases the speed of computation.

For a complete Sigma 3 Computer configuration, two fully expanded basic frame assemblies are used to provide a 64K memory. The second frame of memory, however, requires the No. 1 frame portion in an additional cabinet.

The expansion capabilities of the Sigma 3 Core Memory provide for a very flexible memory unit. A single port user can have access to a core memory ranging from 8K to 64K, several ports can share 64K of memory, or there is the availability of any variation of application in between.

# 1-12. Basic Memory System Expansion

The basic memory system is a fully operational system for controlling the transfer of data in and out of one 8K stack of storage area to one memory port user.

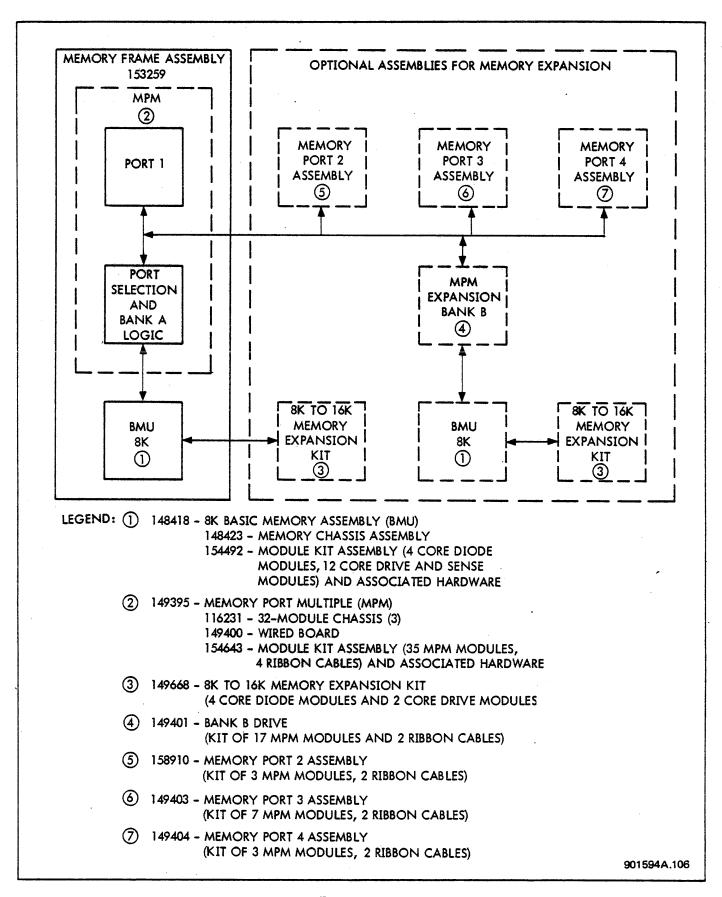

Physically, the Sigma 3 Core Memory system provides for expanding the basic system to a variety of larger memory configurations by the availability of optional module kits. Refer to figure 1-6. The basic memory unit (EMU) is expanded to 16K capacity by the installation of the optional 8K to 16K memory expansion kit. A second 16K bank is added to the memory system by the installation of the optional bank B drive (MPM expansion), an optional BMU and an 8K-16K memory expansion kit. A one to four-way memory access is obtained by the installation of the appropriate optional memory port assembly kits. With this type of expansion capability, two memory

banks of 16K operate independently, and different memory cycles take place simultaneously in the two banks under control of different ports.

# 1-13. MEMORY ADDRESS AND DATA WORD PORMAT

The Sigma 3 Core Memory uses an address word of 16 bits which allows for the addressing of 64K of memory. However, two fully expanded basic memory systems (32K) are required to utilize the entire address field.

The Sigma 3 Core Memory provides storage for a data word consisting of . 16 bits of data and a parity bit.

### 1-14. MEMORY SYSTEM POWER REQUIREMENTS

The memory system utilizes voltage tabs on voltage bus-bar assemblies mounted on the memory frame assembly. Power is available from ene side on the back panel. The voltages are referenced to the power supply ground. The power requirements are as follows:

| VOLTAGE       | MAXIMUM CURRENT | VOLTAGE TOLERANCE |

|---------------|-----------------|-------------------|

| +22 VDC (Nom) | 8.5 amps        | ± 1%              |

| +24 VDC       | 1.8             | ± 1%              |

| +8 VDC        | -8.0            | ± 1%              |

| _8 VDC        | 2.0             | ± 1%              |

| +4 VDC        | 19.0            | <u> </u>          |

Figure 1-6. 8K Basic Memory Frame Assembly and Expansion Capabilities

# 1-15. Power Supplies

Power to the memory system is supplied by the PT-16B and PT-17B power supplies. The PT-16B, located on frame Md. 2 which houses the CPU, supplies the +8V, -8V and +4V for logic circuit operation. These voltages are cabled from the PT-16B power supply to the bus-bar assembly on the memory frame massembly, frame No. 1.

Power supply PT-17B is located on frame No. 1 and supplies a non-adjustable +24V and an adjustable core drive voltage (nom. +22V) to the bus-bar assembly on the frame. The PT-17B is capable of supplying power to two fully expanded BMUS.

### SECTION II

### FUNCTIONAL DESCRIPTION

#### 2-1. INTRODUCTION

The function of the Sigma 3 Core Memory in the Sigma 3 Computer system is dual-purpose; (1) to provide a core storage facility for data, and (2) to provide the means to control the interchange of data between core memory and a memory port user.

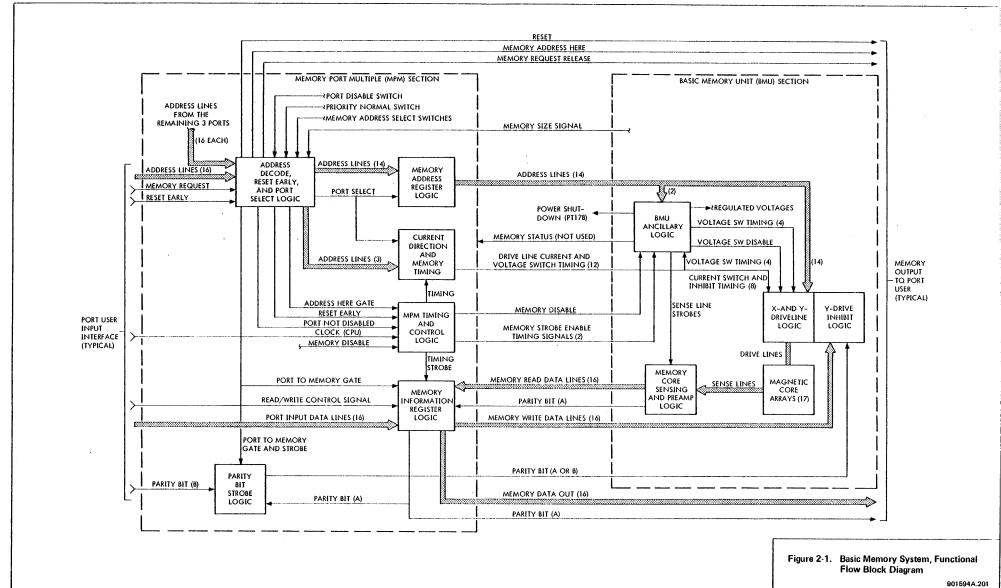

This section describes the logical methods used to perform the required data access and storing function of the basic memory system and follows the functional flow of figure 2-1. To facilitate an understanding of basic memory system operation, the following functional description is divided logically into two sections; the basic memory unit (BMU) section and the memory port multiple (MPM) section.

#### MEMORY PORT MULTIPLE (MPM) SECTION 2**-2.**

The logic assigned to the memory port multiple section of the basic memory system provides the interface to one port, the capability to select multiple port input/output, and to control the data transfer to and from memory bank A (an expanded BMU of 16K.)

The memory address lines (16) from a port user will address two 32K frames of memory (64K). Since the functional description of data flow from one port to one bank of memory is typical for a complete memory system, figure 2-1 shows the interface between one port, port No. 1 and one bank, bank A.

The logic utilized in this section is grouped as follows: Port select, address decode and reset early logic which provides for (1) selecting a particular port for interface with memory (on a port priority basis), (2) for  $\frac{1}{2-1/2-2}$

decoding the address for memory bank selection; and (3) for establishing a memory reset condition; the memory address register logic which supplies temporary storage for the selected memory address during the memory cycle; the memory information register logic which supplies temporary storage for data during the memory cycle; the MPM timing and control logic which provides the memory timing cycle and the port to/from memory data transfer signals; and the current direction and memory timing logic which supplies the timing signals to control the direction and application of core driveline current.

# 2-3. ADDRESS DECODE-RESET EARLY-PORT SELECT LOGIC

A port user requiring the use of the core memory will transmit a memory request signal. At the receipt of this signal the 16 memory address bits, which are also presented by the port user, are examined to determine if the address is within either bank (BMU) connected to the MPM. The basic MPM contains memory address select switches for ports 1 and 2 which define the starting address in terms of 8K increments for two banks of memory and the BMU supplies a memory-size signal (8K or not 8K) which indicates the size of each bank, 8K or 16K. The MPM also contains port disable switches to break with a particular port user.

If the port is disabled, the memory request from the port user is not recognized and also the user reset-early signal cannot reset the memory timing cycle. If the port has not been disabled and the memory address is available, the following events take place: A memory-address-here signal is developed and the memory timing cycle circuitry is enabled in the MPM timing and control logic; a port-to-memory gate is developed to connect the selected port to the selected memory bank and the memory-address-here signal is transmitted to the port user. A port-select transfer signal is also developed for transferring the address bits to logic within the MPM, and after the memory timing

cycle has started a memory-request-release is transmitted to the port user permitting the user to drop the memory request and change the address bits.

The port select logic determines the highest priority port that has an address-here condition, and with the port-select transfer signal, transfers those address bits (14) to the memory address register associated with the bank which is addressed. At the same time, three of the address bits are also selected for decoding by the current direction and memory timing logic.

The MPM has two modes of priority determination between ports; the mode is selected by the setting of the priority-normal toggle switch. When the priority-normal switch is set to normal, port select logic selects port 4, port 3, port 2 and port 1, in this order. If two or more memory requests are received at the same time, the port with the higher priority is processed first, then each one in descending order is processed before any new requests are considered. This prevents high data rate devices from locking out other devices.

When the priority-normal switch is set to a position other than normal, a straight priority scheme prevails where the higher priority port may use every memory access to the exclusion of the other ports.

## 2-4. MPM TIMING AND CONTROL LOGIC

After the address-here condition has been satisfied and the MPM timing and control logic has been enabled, the following events can take place:

If the memory is not busy with a previous request and a port has not

commanded an early reset (return to initial condition) of the timing cycle, the memory timing cycle (read/write sequence) is started at the receipt of the first clock B pulse from the (PU. This clock pulse is used only to synchronize the beginning of each memory cycle; after the cycle has started the memory timing and control is asynchronous.

The MPM timing and control logic provides a timing delay line with the necessary control circuitry. A full timing cycle consists of two consecutive transmissions through the delay line. Pickoff signals at specific time-fromstart points on the delay line establish the time for certain events to take place during the read sequence (first transmission) and the write sequence (second transmission). The pickoff signals determine the on/off time and direction of the driveline current in the BMU as well as time to generate strobe signals for the sense line circuits.

### 2-5 MEMORY ADDRESS REGISTER LOGIC

At the time port priority has been established, 14 of the 16 original address bits from the port user are transferred (by the port-select transfer signal) to the memory address register associated with the addressed memory bank (refer to paragraph 2-3). These address bits enable the X and Y driveline circuitry associated with specific core locations in memory. The addressed bits are latched in the register until the register is reset near the end of the write half cycle of the memory cycle.

### 2-6 CURRENT DIRECTION AND MEMORY TIMING LOGIC

Reading out of or writing in to memory involves the requirement to establish coincident X and Y current at the cores selected for information; part of the address, therefore, determines the direction of each current in relation to the other (both positive or both negative).

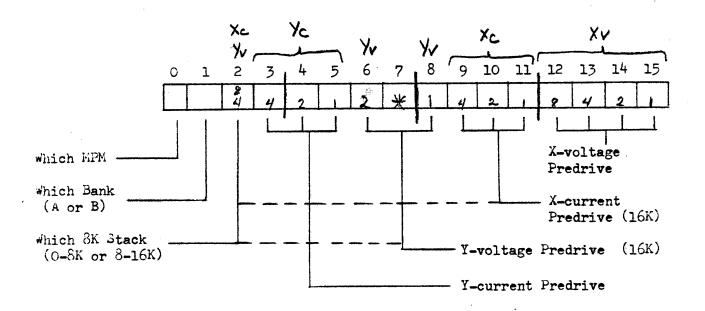

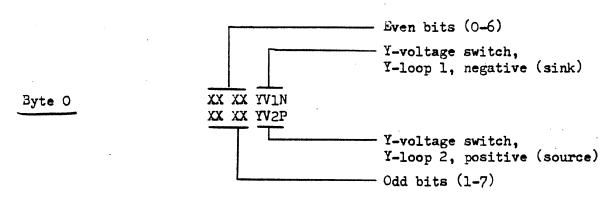

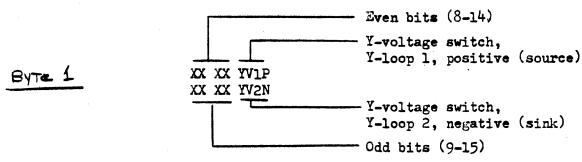

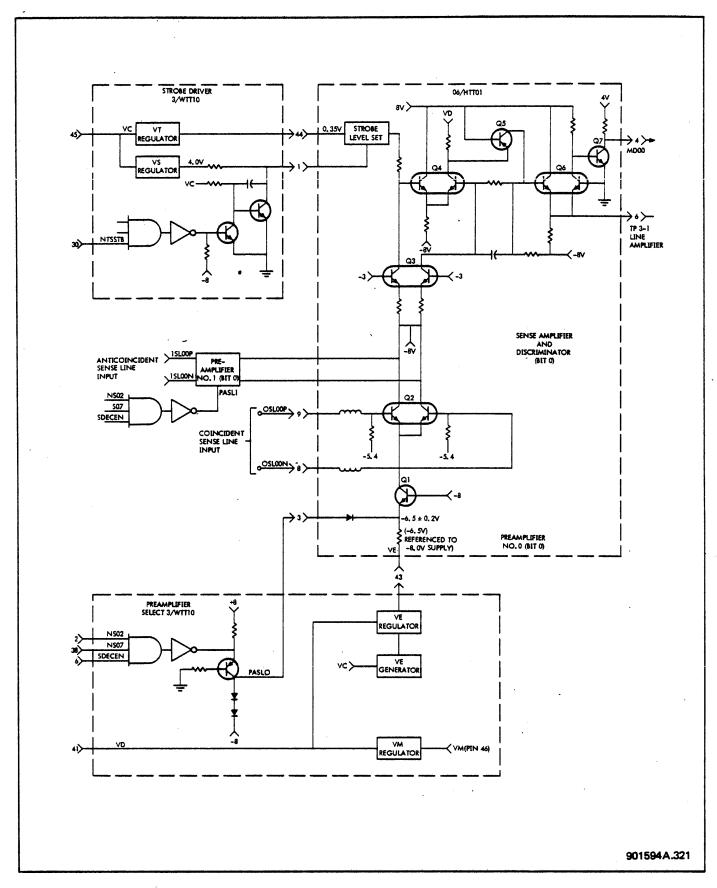

when a port has been selected three bits of the memory address are converted, by the current direction and memory timing logic, to X and Y current direction codes. These codes are transferred by the port-select signal to an X and Y driveline timing circuit within the same logic group. During specific phases of the timing cycle, these codes are used to develop the twelve X and Y driveline timing signals which turn on the positive and negative current and voltage driveline switches in the EMU.

# 2-7 MEMORY INFORMATION REGISTER LOGIC

The memory information register logic group contains a memory information register for temporarily storing 17 bits of data read out of memory or presented by the port user, and additional circuitry for restoring data back into memory or writing new data into memory.

A mode control signal (read or not read) from the user determines the source of data written into core during the write portion of the memory cycle.

At the beginning of the memory cycle, if the logic state of the user's mode control signal is at the level to select the read mode of operation, 17 bits of data are strobed from memory to the memory information register and transferred from the register to the port user. During the write half cycle portion of the memory cycle this data is gated back into memory (data restore operation) through the inhibit circuitry in the BMU.

At the beginning of the memory timing cycle, if the logic state of the user's mode control signal is at the level to select the write mode of operation, the transfer from memory is inhibited during the read half cycle portion; and the 17 bits presented by the user for writing in to memory is transferred, during the write half cycle, through the inhibit circuitry.

The memory information is cleared (reset) near the end of the write half cycle of the memory cycle by the change in the logic levels of the mode-control signal and/or the port-to-memory gate.

### 2-8 PARITY BIT STROBE LOGIC

The parity bit is generated by the user, and since 16 bits of data must be assembled **before** this bit is generated, it lags the data presented and is processed separately. The MPM section provides the circuitry to transfer the parity bit from memory (parity bit A) to the port user, and strobe the parity bit from the user (parity bit B) into memory.

# 2-q. BASIC MEMORY UNIT (BMU) SECTION

The basic memory unit section receives 14 bits of a decoded address on parallel address lines. These address bits locate the core storage area for writing in or reading out information in memory. Two separate groups of data lines are provided for the input and output of 16 data bits (plus parity.) There are no registers in the BMU and therefore the MPM section of the basic memory system performs the storage function of the address and data bits during the memory cycle. The memory cycle (read and write sequence) is controlled by timing pulses generated in logic circuits also provided by the MPM section.

At the beginning of the memory cycle, if the read mode is selected, data is stroped from the cores on the memory read data lines to the selected

port memory information register for output; conversly, if the write mode is selected, data from the cores are blocked during the read portion and, at the beginning of the write portion of the cycle, port input data is transferred to memory on the write data lines.

on the control of the first transfer of the

The BMU employs a 3-wire (X,Y, and sense) memory system or what is known as the 2-1/2 D organization. The system does not have an inhibit wire; the Y wire is common to both core driving and inhibiting.

The logic utilized in this section is grouped as follows: The X and Y driveline logic which drives the magnetic memory cores, the memory sense and preamp logic which provides signal amplification and discrimination when reading out a core, and additional logic necessary to support the drive and sense circuitry.

## 2-10 X AND Y DRIVELINE LOGIC

Each magnetic core represents a bit position in memory and is located by a unique set of X and Y drivelines and each line is driven by bipolar current and voltage switches. Each line carries one-half the current required to change the logic state of the core. Predrive switch circuits, selected by address terms and gated by X and Y driveline timing signals (12) from the MPM section, drive the bipolar current and voltage switches.

Each bit plane has an inhibit circuit which controls current flow through a selected Y driveline, this inhibit action prevents (writes a zero) or allows the writing of a logic one in an addressed core.

The BMU contains protect features which prevent damage to the X and Y driveline circuitry when abnormal airflow, voltage or timing conditions exist. Refer to BMU ancillary logic, paragraph 2-12.

### 2-11. MEMORY CORE SENSING AND PREAMP LOGIC

The logic state of each bit position (core) in a word is sensed by a sense wire threaded through the core together with the X and Y drivelines.

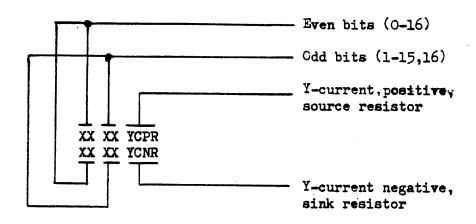

During a read cycle, the address select circuits in the X and Y driveline logic feed current through the appropriate X and Y drivelines. If the currents are additive in either the positive or negative direction the core switches from one polarity (representing a logic one or zero) to the other. This switching of the logic state causes a pulse on the associated sense line. At the arrival of the senseline strobe signals generated in the BMU ancillary logic, paragraph 2-17, the pulse is amplified by the selected preamp circuits, and discriminated and converted by sense amplifier circuits to a convential logic level. These logic levels (data) are fed onto the memory read data lines for memory information retister output to the selected port user and back to the core.

### 2-12. BMU ANCILLARY LOGIC

The BMU ancillary logic provides protect features which prevent damage to driveline switches when power drops below operating limits or timing conditions exist; data-save is also provided. The ancillary logic also augments the drive, predrive and sensing circuitry.

This logic group is mechanized by airflow and voltage monitor circuits, timing pulse protection circuits, a predrive disable circuit, voltage generation and regulation circuits and preamp select and strobe driver circuits.

# 2-13. Airflow and Voltage Monitor Circuits

The airflow monitor circuit senses airflow rate (fan-wane position) of either of two cooling fans installed in the bottom section of the memory frame; and provides a signal to disable the PT-17B power supply (power shutdown signal.)

During power-up or power-down cycle, the memory disable signal from the power monitor circuit is used to override the airflow monitor circuit output. This action prevents false tripping of the PT-17B circuit breaker during a temporary low-fan-power condition.

The voltage monitor circuit senses the value of +8V, +4V, +24V, and -8V supply voltages and causes a predrive disable circuit to be activated when any of these voltages fall below predefined limits. In addition to activating the predrive disable circuit, this monitor allows a memory status signal to go true (memory not operating.) The memory status signal is true when the output of both the voltage monitor and airflow monitor circuits is to the MPM section true. (Note: Although the memory status signal is made available/through the logic contained in the BMU, it is not used in the Sigma 3 configuration.)

# 2-14. Timing Pulse Protection Circuits

Each pair (pos & neg-X or pos & neg-Y) voltage switch timing pulses are guarded against overlap by the provision of delay latch circuits in the ancillary logic. These circuits control minimum spacing between positive and negative timing pulses to prevent damage to the corresponding voltage switches. When switching from a read to a write operation. The latches also prevent damage due to complete loss of timing pulses. An interlock signal grounds the timing pulses in case the ancillary logic module is removed while the power is still applied.

# 2-15. Predrive Disable Circuit

The predrive disable circuit prevents memory accessing by grounding the predrive circuits in the X and Y driveline logic during the following conditions: Power turn-on/turn-off cycles, airflow failure and voltage failure. During power trun-on/turn-off cycles, the memory disable signal activates the predrive disable circuit. The output from the airflow and voltage monitor circuits (paragraph 2-6) activate the predrive disable circuit during airflow failure and voltage failure.

The predrive disable circuit causes data to be saved and damage to the voltage switches is prevented when power drops.

# 2-14. Voltage Generation and Regulation Circuits

The voltage generator and regulator circuits in the ancillary logic provide for the following: (1) Discrimination level voltage (threshold) for the sense amplifiers in the memory core sensing and preamp logic, (2) Start level voltage for the sense amplifier strobe driver, (3) Bias voltage for the current source circuit in the preamplifier circuit, and (4) Bias voltage for the X and Y voltage switches developed from the driveline voltage.

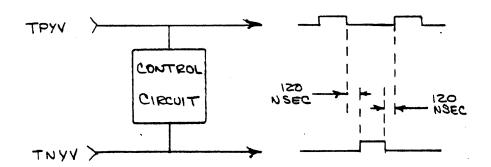

# 2-17. Preamp Select and Strobe Driver Circuits

Two timing pulses from the MPM section (memory strobe enable) are used to activate the preamp select circuit and the strobe driver circuit in the ancillary logic. Two address bits and one of the timing pulses turnon the preamp select circuit which generates one of the sense line strobe signals used in the memory core sensing and preamp logic. The other timing pulse is used to gate the strobe driver circuit which generates the remaining sense line strobe signal. Refer to paragraph 2-11 for application.

of these sense line strobe signals.

### SECTION III

### DETAIL PRINCIPLES OF OPERATION

### 3-1. INTRODUCTION

This section contains detail descriptions of the logic and the mechanization of the logic used in the Sigma 3 Core Memory system in the performance of the required data access and storing functions of the Sigma 3 Computer System.

This section follows the outline of Section II, however, the logic groups are further divided in order to key the detail principles of operation to the Engineering Support Manual (ESM) 902401, Sigma 3 Core Memory (hereafter referred to as ESM 902401). The text content is based, generally, on figure 3-4, Detail Principles of Operation, Block Diagram.

Individual logic diagrams are used throughout the text to support the detailed descriptions of the mechanization of the logic equations contained in Section I of the ESM.902401.

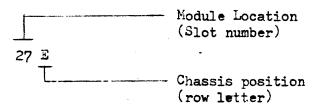

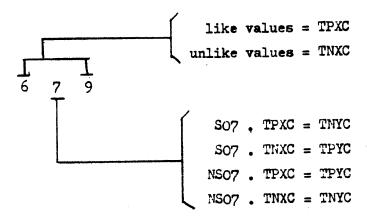

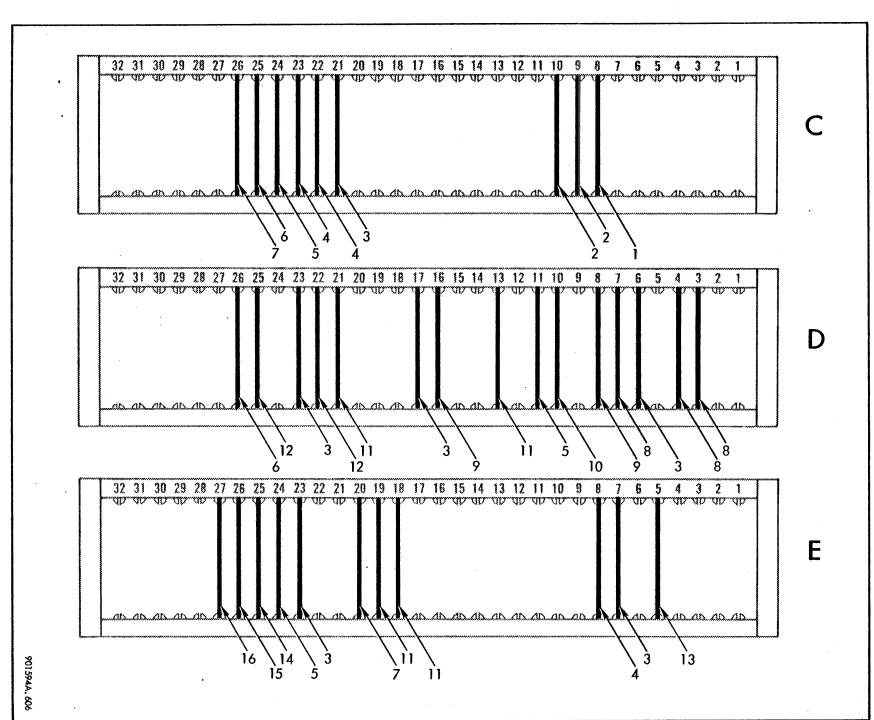

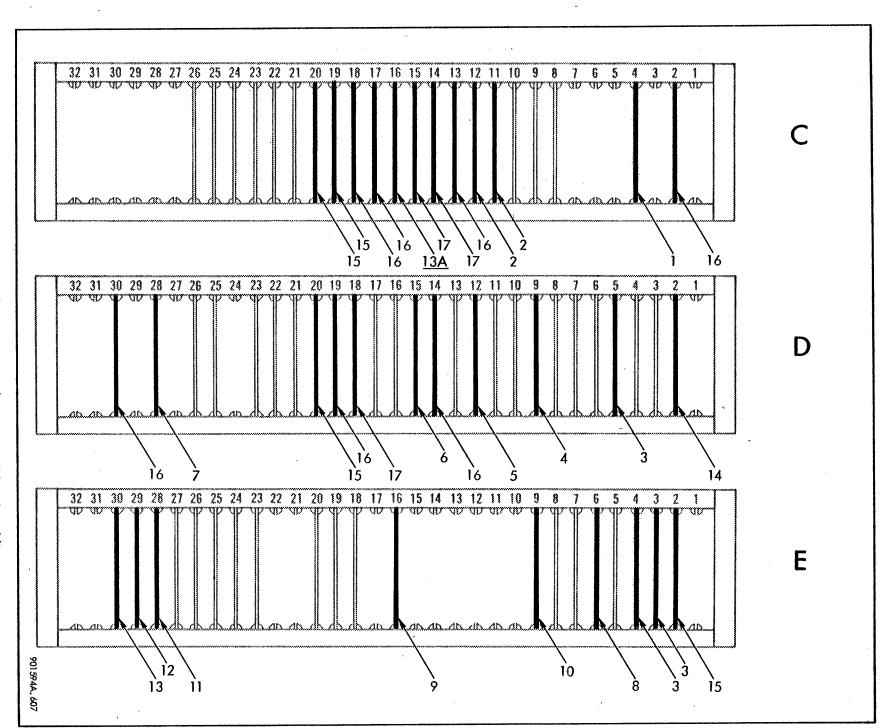

A module location is designated by a code representing the module position number (slot) in the chassis and the chassis position (row) in the frame.

The module slots are numbered (01 - 32) as viewed from the module-insertion side of the chassis. The chassis positions (9) are lettered A through J (excluding I) beginning at the top of the frame. An example of module location is as follows:

In most cases another code is added to the module location code to designate the type of module, as follows:

The information contained in this section pertinent to the Sigma 3 Core

Memory power is general technical coverage. For detail theory of operation

and maintenance refer to the applicable Data Package for the PT-14B,

PT-15B, PT-16B and PT-17B power supplies; 901655, 901656, 901657 and

901658, respectively.

# 3-2 SIGMA 3 POWER DISTRIBUTION

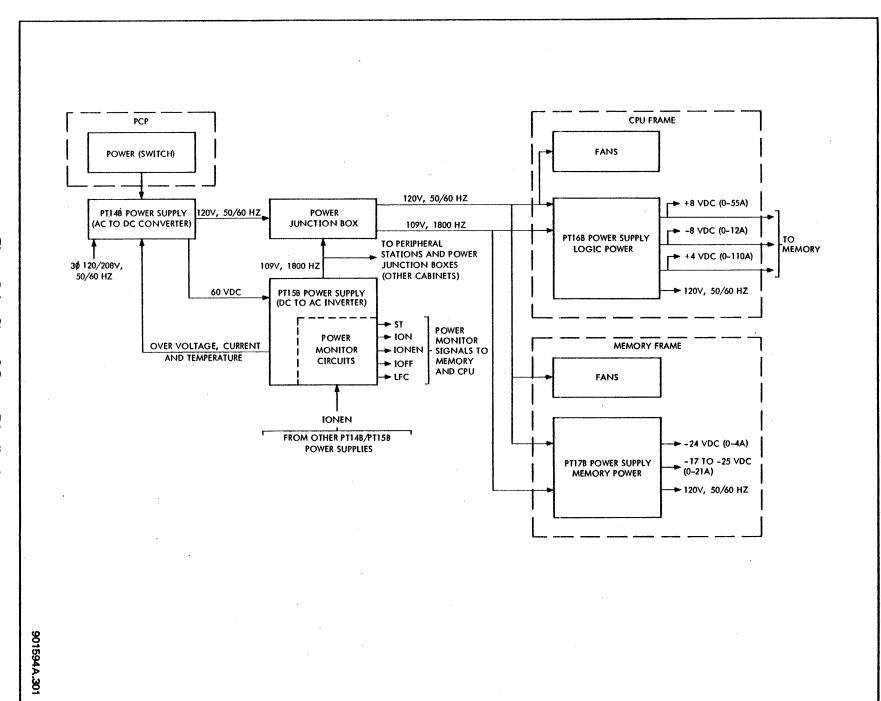

Figure 3-1, a block diagram of the Sigma 3 Power Distribution, in included in this section in order to show the position of the Sigma 3 Core Memory in the overall power supply structure.

Figure 3-1. Sigma 3 Power Distribution

when the POWER switch on the Sigma 3 Computer system processor control panel (PCP) is pressed, 3 phase, 120/208V, 60 mHz, facility power is applied to the first internal power supply, PT-14B. The PT-14B supply converts the facility power to 60 VDC to power the PT-15B power supply. Also, a 120V, 50/60 mHz output from the PT-15B is cabled to a power junction box for distribution within the system.

The PT-15B power supply converts the 60VDC to an ac voltage of 109V, 1800 mHz which is connected to the power junction box for distribution to the PT-16B and PT-17B power supplies. This voltage (109V, 1800 mHz) is also available to peripheral stations and the power junction box in other cabinets of the computer system.

The PT-15B also contains circuitry which monitors overvoltage, overload and fan failure. When anyone of these conditions prevail, the main circuit breaker in the PT-14B is opened, disconnecting the facility power. If the power fail safe option is included in the Sigma 3 System, PT-15B will contain power monitor circuits. Refer to paragraph 3-3 for detail description.

The 120V, 50/60 mHz junction box output is used to operate the fans on the CPU and memory frames and is available as auxiliary power for other general applications.

The PT-16B power supply converts the 109V, 1800 mHz power from the PT-15B to regulated dc power for logic circuit operations. The dc output is +8 V, ,-8 V, +4 V and is made available to all logic circuits in frame No. 2 through bus-bar assemblies mounted on the frame.

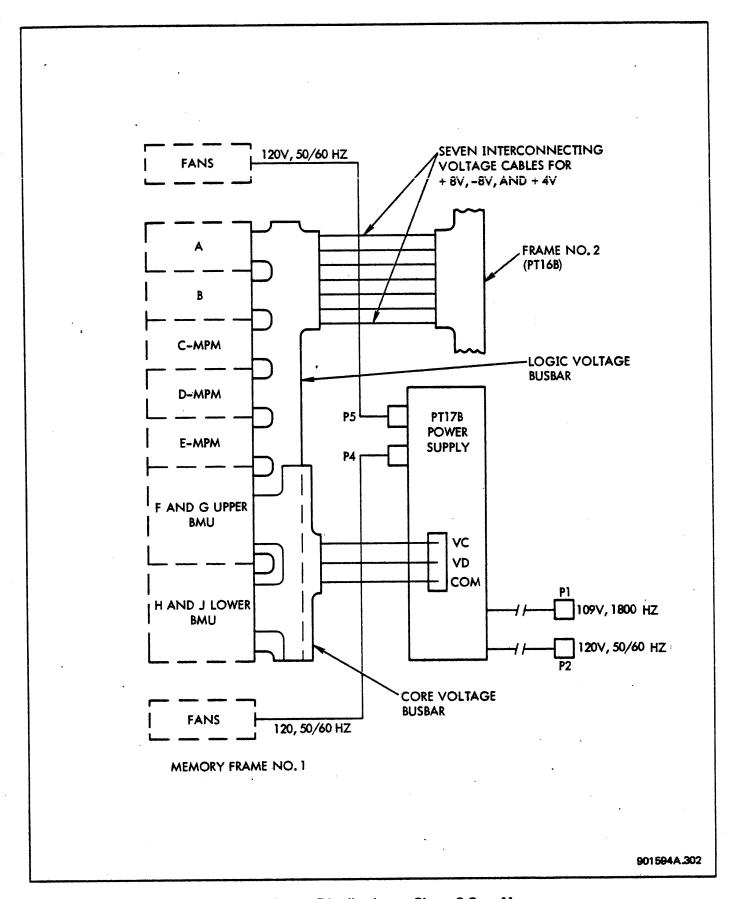

Two pig tails terminating in connectors F1 and F2 from the PT-17B power supply (refer to figure 3-2) are connected to 109V, 1800 mHz and 120V, 50/60 mHz, respectively, from the system junction box. PT-17B converts the 109V, 1800 mHz to two regulated dc voltages. One voltage is VC, a non-adjustable +24 volts used for the predrive circuits in core memory. The other, an adjustable nominal +22 volts is used to drive the X and Y drivelines in core memory. These voltages are distributed to both BMUS via the core voltage bus-bar. The 120V, 50/60 mHz is routed out through connectors =5 and P4 to the upper and lower frame-ventilating fans.

The memory logic circuit operating voltages are cabled (7) from the voltage bus-bar on frame No. 2 from the PT-16B power supply. These logic operating voltages are distributed to all chassis in the memory frame (No. 1) via the logic voltage bus-bar.

#### 3-3 MEMORY PROTECT FEATURES

During power turnon/turnoff or failure the power monitor system (optional) generates signals which provide for the selection of two interrupt levels (CPU option), a system reset-early sequence (MPM), as well as a signal to the predrive disable circuit in the BMU to protect the voltage switches in core memory.

The predrive disable circuit is also enabled when a voltage monitor circuit in the BMU detects the dc power supplies have dropped below the following

+8V supply ≤ +6V +4V supply ≤ +3V -8V supply ≤ -4V +24 supply ≤ +20V

The voltage monitor circuit operates independent of the power monitor system output.

Figure 3-2. Power Distribution to Sigma 3 Core Memory

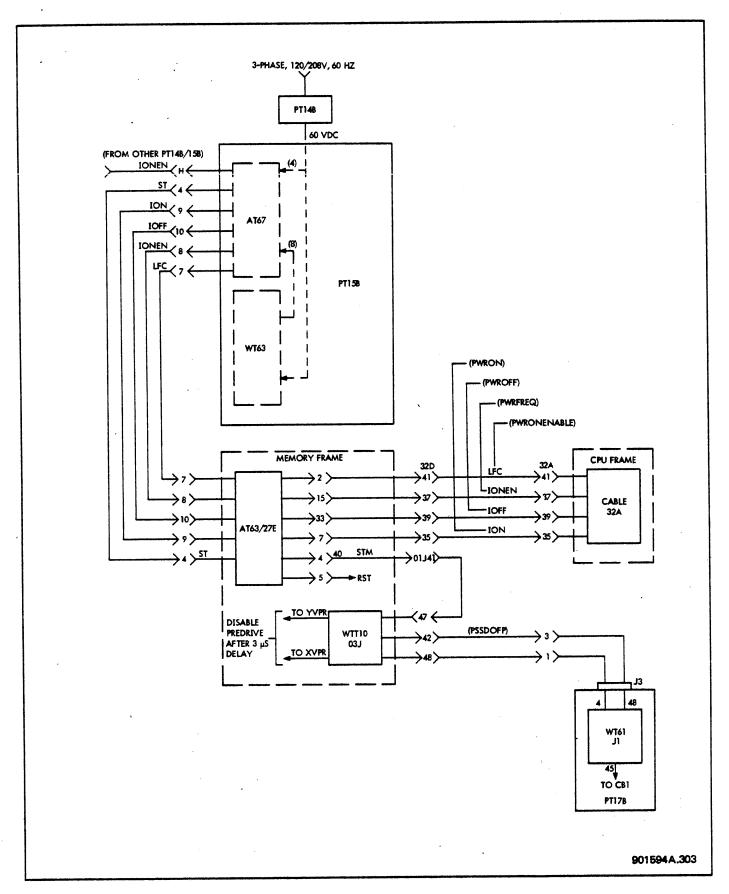

#### 3-4. POWER MONITOR SYSTEM

Refer to figure 3-3. The 60 VDC input to the PT-15B power supply is monitored, which in effect, is monitoring the facility input power to the PT-14B power supply. When power is turned off or there is a power failure, IONEN (power-on enable interrupt) and IOFF (power-off interrupt) are true. IOFF is true for 5 milliseconds during which time the CPU performs a software interrupt subroutine to store all volatile registers to prevent critical program loss. At the end of 5 milliseconds, an ST (start/stop) signal goes true and stays true until the output of the dc supplies have decayed to a minimum of 15% of the initial values.

The ST signal is one of two possible input signals to the reset-early circuit (paragraph 3-10) in the AT63 module in memory (MPM) where it initiates the reset-early sequence. During the reset-early sequence, memory port input is inhibited and latches are dropped on MPM timing logic. The ST signal is also applied to a special line receiver circuit in the WTT10 module (BMU). This circuit prevents damage to the predrive voltage switches (when power is unstable) by grounding the drive voltage (VC) at predrive resistors, YVPR and XVPR. Refer to ESM 902401, drawing No. 153726, sheet 4, for further details.

When power starts up (or turned on) ST goes true and after 3 microseconds STM enables the predrive disable circuit. ST stays true until the dc power supplies are stabilized (1 to 3 seconds). When ST goes false, ION (power-on interrupt) is true and the CPU performs a subroutine to restore all critical conditions existing prior to the power-off state.

The LFC (PWRFREQ) line frequency clock is the output of a schmitt trigger circuit in the AT67 module and can be used as imput to counters, 4, 3, and 2 in the CPU internal priority interrupt system.

Figure 3-3. Sigma 3 Power Monitor System (Power Fail-Safe) and PT17B Shutdown

## 3-5. PT-17B SHUTDOWN

The BMU provides an airflow monitor circuit which monitors the temperature of the lower memory frame fan area. The output of two thermistor circuits installed on the WTT10 module is input to the monitor circuit. When the monitor senses airflow failure (rise in temperature) PSSDOFP (which is normally false) goes true and turns on a circuit in the VC and VD overvoltage monitoring circuit on the WT61 module in the PT-17B power supply. (Refer to the associated ESM, Section II, drawing No. 153726, sheet 4.) A subsequent pulse generated by the overvoltage circuit triggers the SCR in the PT-17B power supply which in turn triggers the circuit breaker (CB1).

The ST signal from the power monitor system (paragraph 3-3) is also used to keep PSSDOFP low during power turnon/turnoff sequence and therefore not trigger the PT-17B circuit breaker if the airflow fails at this time.

#### 3-6. SIGMA 3 CORE MEMORY LOGIC

Sigma 3 Core Memory logic is documented in Section III of this manual and in ESM 902401. The circuit diagrams in this section are keyed to the line numbers in the Logic Equations, Pin List and Pin Index in Section I of the associated ESM. The text contained in this section is referenced to information contained in Section II of the ESM 902401 for Logic Glossary and further details pertinent to circuit descriptions.

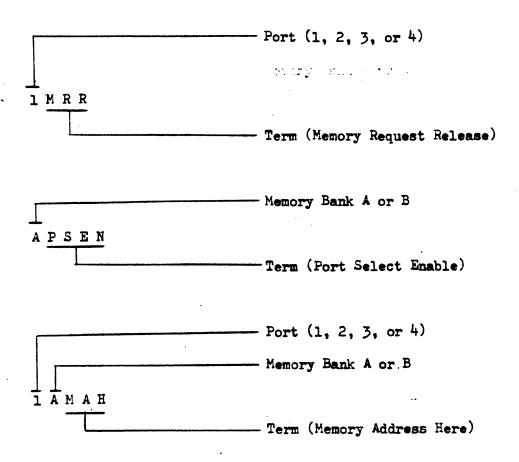

Figure 3-4, Detail Principles of Operation, Block Diagram, is an overall representation of the logic involved in the Sigma 3 Core Memory. Primary internal and interface terms associated with the system are shown. Terms at the port interface are enclosed within two diagonal lines / /. The first character, if a number in the complete term, represents a port (1, 2, 3, or 4); or if a letter, the letter represents a memory bank (A orB). The second character, if A or B and preceded by a port number, is the

memory bank A or B. Three typical complete logic terms are:

The letter N preceding a complete term designates the negation of the term.

# 3-7. SIGNAL DISTRIBUTION

Refer to MPM Cable Table ESM 902401, Section II, drawing 155369, MPM Module Location Chart 153272, and BMU Module Location Chart 153726.

The major portion of signal distribution, externally between a user and a memory port and internally between the MPM and BMU sections, is achieved through ribbon cable assemblies. Two ribbon cable assemblies (ZT45), terminating in etched-circuit boards at right angles to the cables, distribute signals between the MPM and BMU sections (two for each, bank A and bank B). The ribbon cables extending from OlD to OlH and OlF to OlJ distribute the signals listed in the Interface Table in 153726.

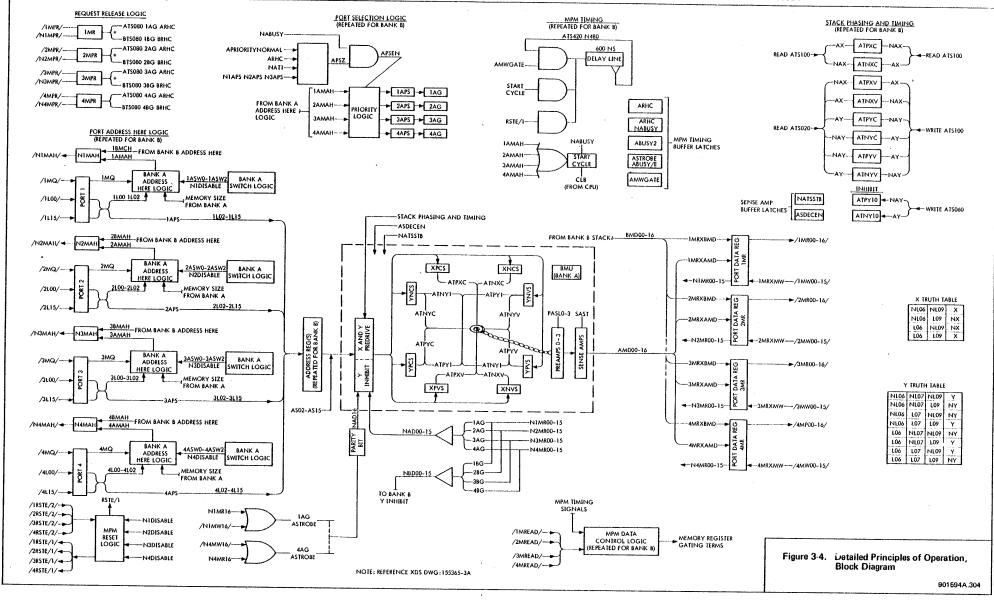

The major portion of the MPM logic is mechanized using the 309 buffered latch. Figure 3-5 includes a logic diagram showing the AND/OR input to a typical buffered latch and a general description of circuit operation. All registers, the major portion of the MPM timing and control logic and stack phasing (current direction) logic are mechanized using the 309 buffered latch.

Figure 3-5. Buffered Latch, 309

# 3-9 ADDRESS DECODE (PORT ADDRESS-HERE) LOGIC

Fort address-here logic is implemented separately for each port and bank connected to an MPM so that any port can connect to any bank, independently. The logic descriptions for one port and one bank are identical for all ports and both banks, therefore, the following description covers port 1 connected to bank A.

The input to port address-here logic is as follows: (1) memory request /IMQ/ and the most significant address lines /ILOO - ILO2/ from the port user, (2) starting address information for each port from switch logic (1ASWO - 1ASW2), (3) not-port disable (N1DISABLE) information from switch logic and (4) memory bank size information, 8K or not 8K (16K) from the BMU section.

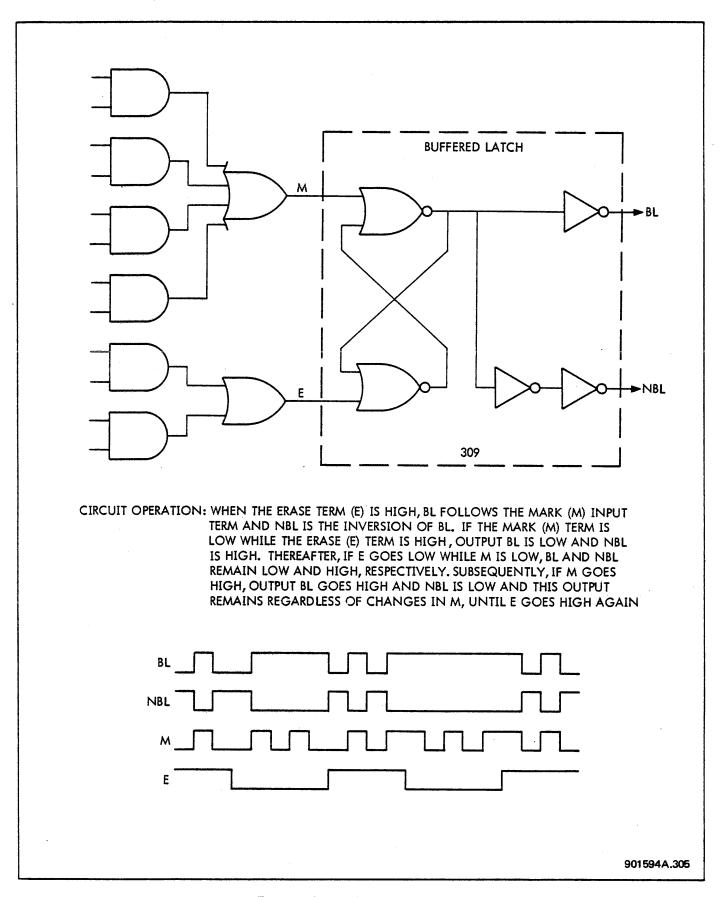

Refer to figure 3-6. An ST14 module in position O8C provides the toggle switches for switch logic input to the address decode logic for bank A. Three switches, each, are provided for ports 1 and 2 for setting the starting address for each port for bank A of memory. Two switches are provided to disable port 1 or 2, if required. Table 3-1 provides a reference for switch designations and locations for a complete system of 4 ports and 2 banks.

Table 3-1. Port Address-Here Switch Designations and Locations

| MPM: 1 or 2 | Port | Switch No. For Starting Address SWO SW1 SW2 |    | Switch No. For Port Disable | Module<br>ST14<br>Location | Switch No. For<br>Priority-<br>Normal |           |  |

|-------------|------|---------------------------------------------|----|-----------------------------|----------------------------|---------------------------------------|-----------|--|

|             | 1    | 5                                           | 4  | 3                           | 15                         | 080                                   |           |  |

| Benk A      | 2    | 9                                           | 8  | 6                           | 1                          | 08C                                   | 2 on 08C  |  |

|             | 3    | 5                                           | 4  | 3                           | 2                          | 02C                                   | 2 01 080  |  |

|             | 4    | 9                                           | 8  | 6 .                         | 15                         | 020                                   |           |  |

| Bank B      | 1    | 5                                           | 4  | 3                           | -                          | 04C                                   |           |  |

|             | 2    | 9                                           | 8  | 6                           | -                          | 04C                                   | 14 on 08C |  |

|             | 3    | 2                                           | 1  | 11                          | -                          | 04C                                   | 14 OH OGG |  |

|             | 4    | 15                                          | 14 | 12                          | -                          | 04C .                                 |           |  |

Table 3-2. Port Address-Here Decoding

| Memory Address           |                    | · Starting Address |     |     | Bank Size L-Lines |    | 6  |            |

|--------------------------|--------------------|--------------------|-----|-----|-------------------|----|----|------------|

| Decimal                  | Hexidecimal        | SWO                | SW1 | SW2 | Term ASK/BSK      | 0  | 1  | 2          |

| 0-8191                   | 0000-1FFF          | 0                  | 0   | o   | High              | ٥  | ٥  | ٥          |

| 0-16383                  | 0000-3777          | 0                  | ٥   | 0   | Low               | 0  | o  | ٥          |

|                          | 333                | _                  | 7   |     |                   |    | or | •          |

|                          |                    |                    |     |     |                   | 0  | 0  | 1          |

| 8192-16383               | 2000-3777          | 0                  | 0   | 1   | Low               | 0  | 0  | 1          |

| 16384-24575              | 4000 <b>-5777</b>  | 0                  | 1   | 0   | High              | 0  | 1  | 0          |

| 16384-32767              | 4000 <b>-7333</b>  | 0                  | ı   | 0   | Low               | 0  | 1  | <b>o</b> . |

|                          | ·                  |                    |     |     |                   |    | or |            |

|                          |                    |                    |     |     |                   | 0  | 1  | 1          |

| 24576-32767              | 6000 <b>-7777</b>  | 0                  | 1   | 1   | Low               | 0  | 1  | 1          |

| 32768-40959              | 8000 <b>-</b> 9FFF | 1                  | 0   | 0   | High              | 1  | 0  | 0          |

| 32768-49151              | 8000-BPF <b>P</b>  | 1                  | 0   | 0   | Low               | 1  | 0  | 0          |

|                          |                    |                    |     |     |                   | or |    |            |

|                          |                    |                    |     |     |                   | 1  | 0  | 1          |

| 40960-49151              | Acco-Byfy          | 1                  | 0   | 1   | Low               | 1  | 0  | 1          |

| 49152-57343              | COOC-DFFF          | 1                  | 1   | 0   | High              | 1  | 1  | 0          |

| 49152-65535              | COCO-FFFF          | 1                  | 1   | 0   | Low               | 1  | 1  | 0          |

|                          |                    |                    |     |     |                   | or |    |            |

|                          |                    |                    |     |     |                   | 1  | 1  | 1          |

| 5 <del>7344-6</del> 5535 | ECCO-PFFF          | 1                  | 1   | 1   | Low               | 1  | 1  | 1          |

|                          |                    | 1                  |     |     |                   |    |    | ŀ          |

All input to the address decode portion of the port address-here logic must establish a false condition to have selected a legal address in bank A. Refer to table 3-2 showing the address-here decoding method. Table 3-2 is used in conjunction with figure 3-6, in the area showing module 26D/IT24.

The following is an example of conditions used to determine a legal address. Assume the following input to the address decoding logic: NlASWO, NlASWI and NlASW2 indicating a starting address of zero. The A8K term from the BNU is low (bank A contains a full 16K). The L-lines are NlLOO, NlLO1 and lLO2. Under these conditions not one of the input AND conditions is satisfied, therefore the address is legal. However, if the A8K term is high indicating bank A has only 8K, the AND condition NlASW2.1LO2.A8K is satisfied, therefore the address is illegal and lAMAH is inhibited.

when the address decode has determined a legal address, the lAMAH term can go high if there's a memory request, the port is not disabled and a resetearly has not been generated. The LAMAH term is used as input to the memory-start cycle logic in memory timing and control logic and as input to the priority logic in the port selection logic.

The laMAH or lBMAH terms is selected as the lMAH output to the port user through a buffered latch on OSE. The inversion of lMAH is also sent to the port user.

# 3-10. RESET-EARLY LOGIC

Reset-early logic inhibits memory access and initializes all logic in the MPM section. The reset-early logic also provides signals to the port user to reset internal logic.

There are several donditions which could occur in the Sigma 3 Computer System operation which would cause reset-early (RSTE/1/ - /4) to go high.

RSTE/2/1 - /4 is generated and reset-early is initiated when the RESET button on the PCP panel of the CPU is pressed or the automatic reset feature on the PCP panel is utilized, or a system reset is generated by users on ports 2, 3, or 4. Also if the power monitor system option has been included in the system the ST term from the monitor system will initiate an RSTE/1.

In any of the previously described conditions, the arrival of an RSTE/2 or an ST at the reset-early logic will initiate the following sequence of events (refer to reset-early timing diagram on figure 3-6:) RSTE/2 or ST is high at the input to reset-early logic and also to a 5 microsecond delay line in module 27E/AT63. After a 1.5 microsecond delay RSTE/1 goes high and remains high for a minimum of 5 microseconds or as long as RSTE/2 or ST remain high. RSTE/1/1 - /4 are used by the associated port user to control internal logic.

During the time RSTE/l is high, NRSTE is low thereby inhibiting MAH for all ports. Also, during the time RSTE/l is high, RST is high and lifts all latches on all MPM timing terms. RST-l through 4 are used by the associated port user to reset internal logic. RST-5 holds NRST low; NRST is used to disable certain key timing signals (refer to equations at lines 0151300 and 0151800 in Section I of the ESM). With NRST low ARHC is not

generated, APS/E is high (refer to figure 3-9) and the latches are reset on all port select and memory address register logic as well as current phasing logic; also memory strobe signals are inhibited. RST-6 resets the latches on all port-to-memory gates (AG).

While RSTE/1 is high, at each clock B (approximately every 325 nanoseconds) the memory timing delay line is restarted (refer to figure 3-7). This recycling of the memory delay line is to insure all timing latches are initialized (the mark input low) when the erase term (RST) goes low again.

Within 500 nanoseconds after RSTE/2 or ST goes low, RSTE/1 is low. At the next clock A, NRSTE goes high, and at the following clock B, NRST goes high; when NRSTE is high the memory may be accessed again.

#### 3-11. MPM TIMING AND CONTROL LOGIC

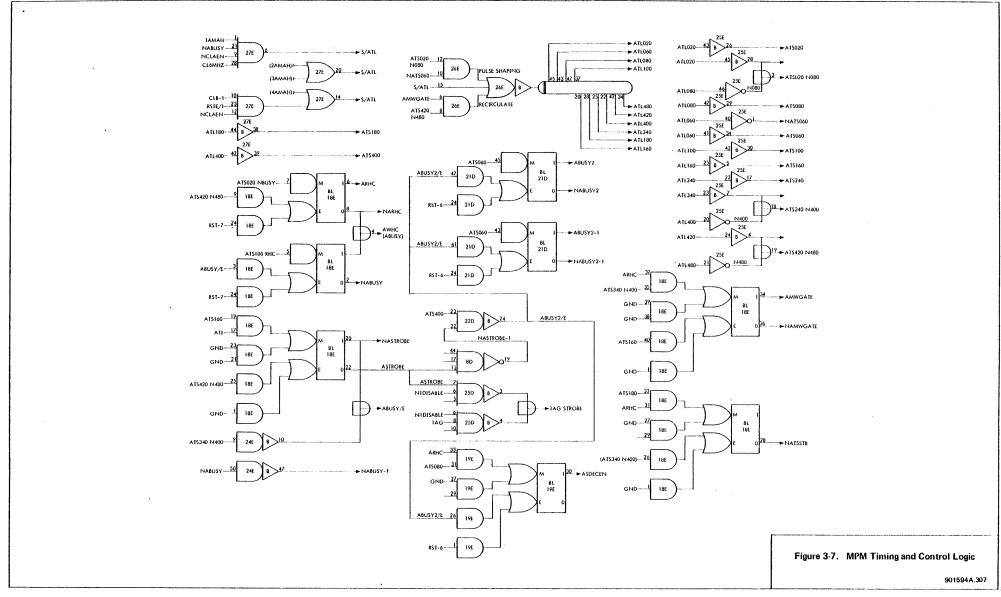

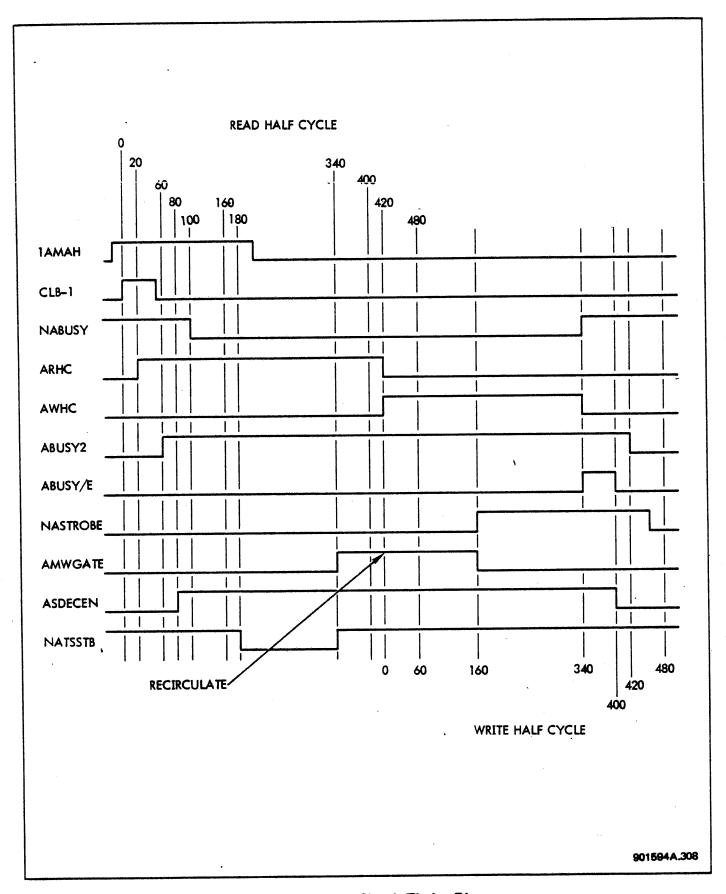

The MPM timing and control logic provides the overall synchronization for a memory cycle. The circuitry consists of a 600 nanosecond delay line, the delay line sensors and 309 buffered latches for control signal generation. The Sigma 3 MPM provides separate timing and control logic for each bank connected to an MPM.

The memory cycle is divided into two halves; the first half is the read half cycle, the last half, the write half cycle. The two half cycles are provided by recirculating the delay line at the end of the read half cycle. Each memory cycle always consists of a full read half cycle followed by a full write half cycle. There is no provision for a partial cycle.

The delay line is tapped at specific intervals (between ATLO20 - ATL480) and these taps are sensed by delay-line sensors, the output of which (ATSO20 - ATS420.N480) is applied to buffered latches. The buffered latches provide the MPM control terms.

Refer to figure 3-7 and 3-8. The memory timing sequence is as follows:

The previous cycle ended with NABUSY latched high. If a legal address

(ANAH) has been established in the port address-here logic, start-A-time

line (S/ATL) will go high at the arrival of a clock B pulse and the delay

line is started. The clock B pulse is derived from not-clock-A enable (NCLAEN)

and the 6 MHz pulse, both from the CPU, and is used only to synchronize the

beginning of each memory cycle. After the cycle has started, the memory

timing and control is asynchronous.

Output ATSO20.NO80 from delay line sensors are returned to the input of the delay line to develop a theoretical delay line pulse width of 60 nanoseconds.

Figure 3-8. Control Signals Timing Diagram

In actual pratice, however, logic and other circuit delays will cause the delay line pulse width to range between 90 and 120 nanoseconds. The MPM timing diagram in Section II, drawing No. 155365, sheet 7, of the ESM is by derived/taking this tolerance into consideration.

The read half cycle (ARHC) is actually started at ATSO20; ARHC goes high when NRST.NABUSY.ATLO20 (0151300) are all high and is latched high until ATS420 of the read cycle. ABUSY2 goes high at ATSO60 of the read cycle and the inversion of this term (NABUSY2) is used to control the buffered latches in the port select and memory address register logic (figure 3-9). The term NABUSY2 enables the port-to-memory gate (AG) to enable the selected port to control the associated memory information register (MR), as well as latch the current direction (stack phasing) logic (figure 3-12).

At ATSO80 of the read cycle sense-decode enable (ASDECEN) is high to enable the preamp select circuit in the BMU. At ATS100, NABUSY goes low causing the port-select enable (APSEN) term to go low inhibiting further port the selection during/memory cycle (refer to port select logic paragraph 3-11.)

At ATS180 in the read cycle, not-time-for sense strobe (NATSSTB) goes low to the strobe driver circuits in the BMU and, at a point between ATS180 and ATS340 data is strobed from the sense lines onto the AMD lines in the selected port memory information register (MR). With ASTROBE high at ATS420, 1AG.STROBE is high and data is gated to the selected port user if the read mode of operation was selected.

At (ATSA20.N480), NARHC goes high and pulls the write half cycle term (AWHC) high. The AWHC term is latched high with ABUSY/E held low by NASTROBE.

Also at ATS420, with memory write gate (AMWGATE) previously latched high, the delay line is recirculated (starting at T zero); this is the start of

the write half cycle. At this time, if the write mode of operation was selected, data from the port user (MW) is transferred to the MR.

At ATS160 in the write half cycle, NASTROBE goes high enabling ABUSY/E to go high at ATS340.NS400. When ABUSY/E goes high the latch is dropped on AWHC and NABUSY. With NABUSY high, a new memory cycle can be initiated.

A start-A-time delay line (S/ATL) can be generated when lAMAH is inhibited during a reset-early (RSTE/1) sequence as described in paragraph 3-10.

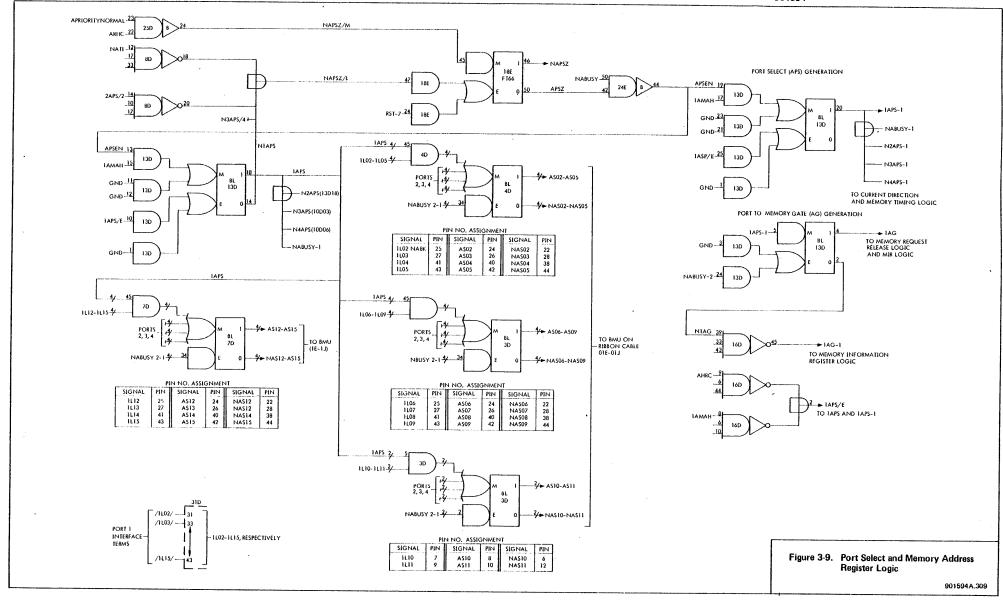

# 3-12 PORT SELECTION AND MEMORY ADDRESS REGISTER LOGIC

It is possible that all four ports will present memory requests (MQ) simultaneously to the same bank and memory address-here conditions can be established for all ports. Since only one port may access memory at a time, the port selection logic is repeated for each bank connected to an MPM. The output of the port selection logic (APS and AG) are gating signals with the primary purpose to enable memory address and data transfers between the selected port and the correct bank.

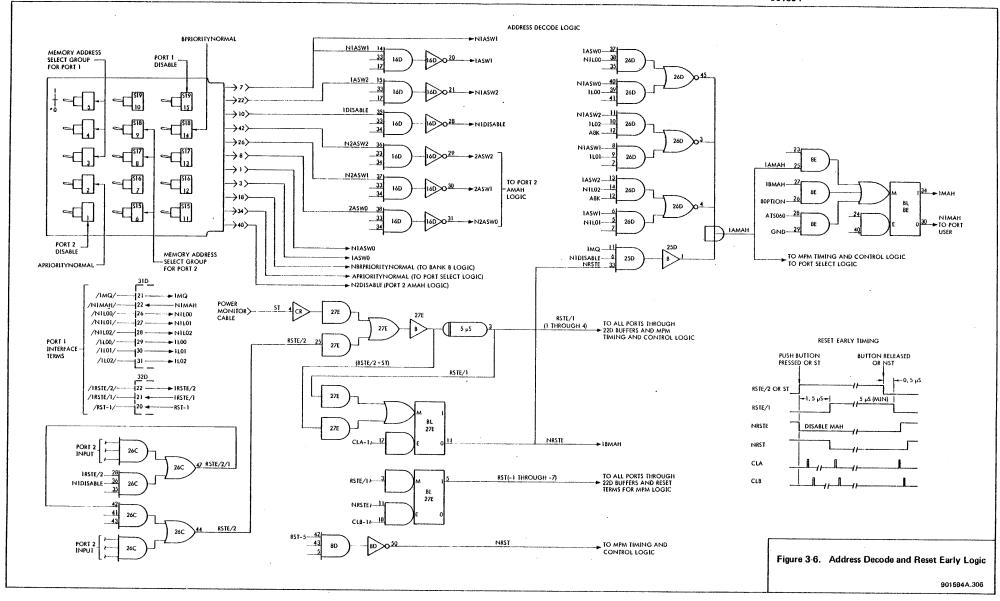

Port priority is established in one of two modes depending on the position of the APRIORITY-NORMAL switch located on card OSC (refer to figure 3-6.)

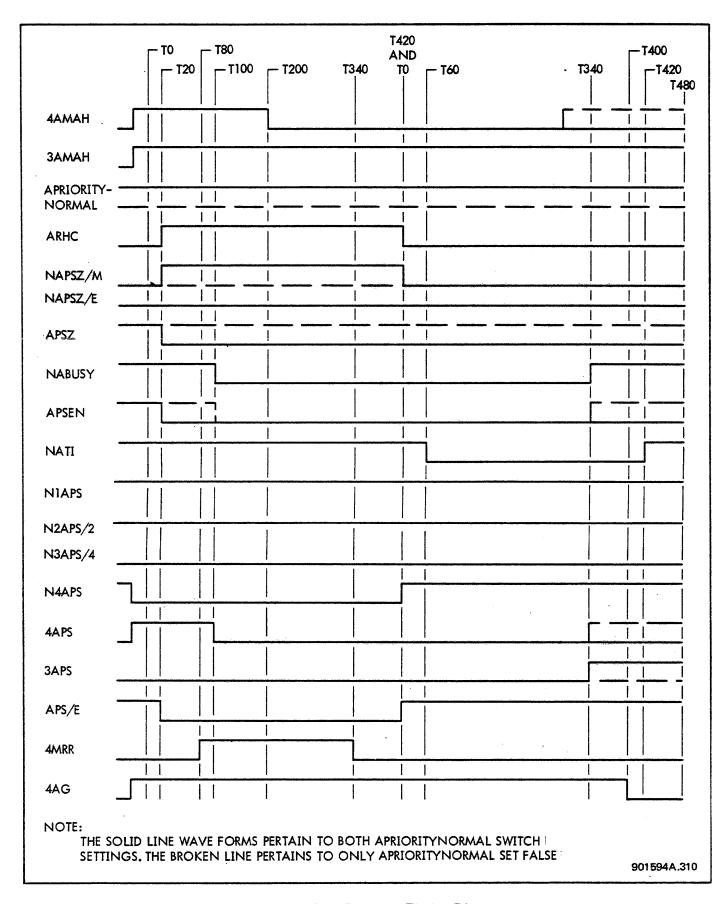

## 3-13. APRIORITY-NORMAL True

In the true position (down) the APRIORITY-NCRMAL toggle switch selects the port priority mode which effectively selects all ports, with an AMAH pending at one time, and connects each in a priority sequence until the lowest priority port has been serviced. In the event of two simultaneous requests, the lower priority will wait only a maximum of one full memory cycle

(in addition to the remaining portion of the current cycle, if any) after raising the memory request line.

Refer to figure 3-9, 3-10 and 3-11. At the end of a memory timing cycle, NAPSZ/E is low due to NATI (not-A-time inhibit) going high. NAPSZ is low since one of the conditions satisfying the mark input (ARHC) is low causing APSZ to be high. NABUSY was latched high near the end of the previous memory cycle and this condition allows the APSEN term (port-select-enable for bank A) to go high. Assume two address-here conditions are simultaneously met; 3AMAH and 4AMAH. Raising 4APS (0087300) depends on only APSEN, 4AMAH and NABUSY-1 to be high, therefore port 4 is serviced first and the L-lines (/4LO2 - /4L15/) from port 4 are latched in the memory address register for bank A. At thereame-time the port-to-bank A memory gate (4AG) is latched high by NABUSY2 (low) and 3APS is held low by the inverted 4APS term (N4APS).

A memory cycle started with 4AMAH high and, at ATSO2O, ARHC goes high making the mark input to NAPSZ high, causing APSZ to drop low. When APSZ is low portselect enable (APSEN) is low and Ehrometer of another port priority sequence is inhibited.during this memory cycle. At ATS100 the latch is dropped on NABUSY bringing term 4APS low; port 4 can change address lines in anticipation of the next request.

With 4AG and ARHC high, memory request release (4MRR) is high to the port user at ATSO80 (figure 3-11). After the arrival of /4MRR/, the port user will drop the memory request (4 MQ) before the end of the read cycle (NRHC) at ATS420; dropping 4MQ will cause 4AMAH to drop. At ATS420 APS/E goes high to lift the latches on all port APS terms. However, only N4APS goes high since N1APS and N2APS are already high and N3APS/4 is latched low by 3APS/E; 3APS/E is held low by the 3AMAH term remaining high.

Figure 3-10. Port Selection Timing Diagram

Figure 3-11. Memory Request Release Logic

when ARHC goes low at the end of the read cycle, the mark input to NAPSZ goes low. The NAPSZ reset term NAPSZ/E does not change state when NATI goes low at ATSO60 of the write cycle due to N3APS/4; this condition keeps APSZ low which will keep APSEN disabled. With APSEN low, if port 4 tries another request during the current cycle, it will not be serviced. When NABUSY goes high at ATS340 in the write cycle, 3APS will go high and the address lines (ASO2 - AS15) will reflect port 3 L-lines when NABUSY2 goes high at ATS400. Also, when NABUSY2 goes high the latch is lifted on 4AG, removing port 4 from memory and 3AG goes high connecting port 3 to memory.

The next memory cycle starts with the remaining 3AMAH still high; APSZ and APSEN are still low and with the port-select enable term low, port 4 is inhibited from service. After /3MRR/ is sent to port 3 at ATSO80 of the read cycle, port 3 will cause 3AMAH to drop low before ARHC goes low at ATS420. With both 3AMAH and ARHC low, 3APS/E will go high, lifting the latch on N3APS/4. When NATI goes low at ATSO60 in the write cycle, all conditions to satisfy NAPSZ/E will be met and APSZ will go high. With APSZ high when NABUSY goes high at ATS340, APSEN will go high allowing the initation of another port priority sequence.

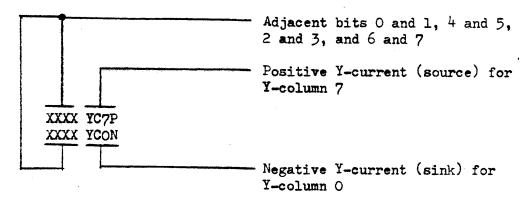

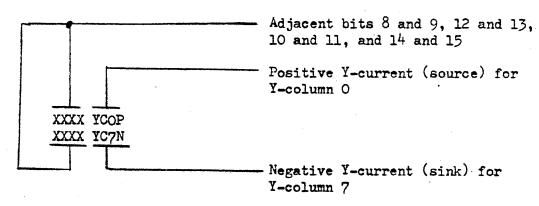

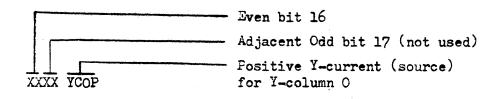

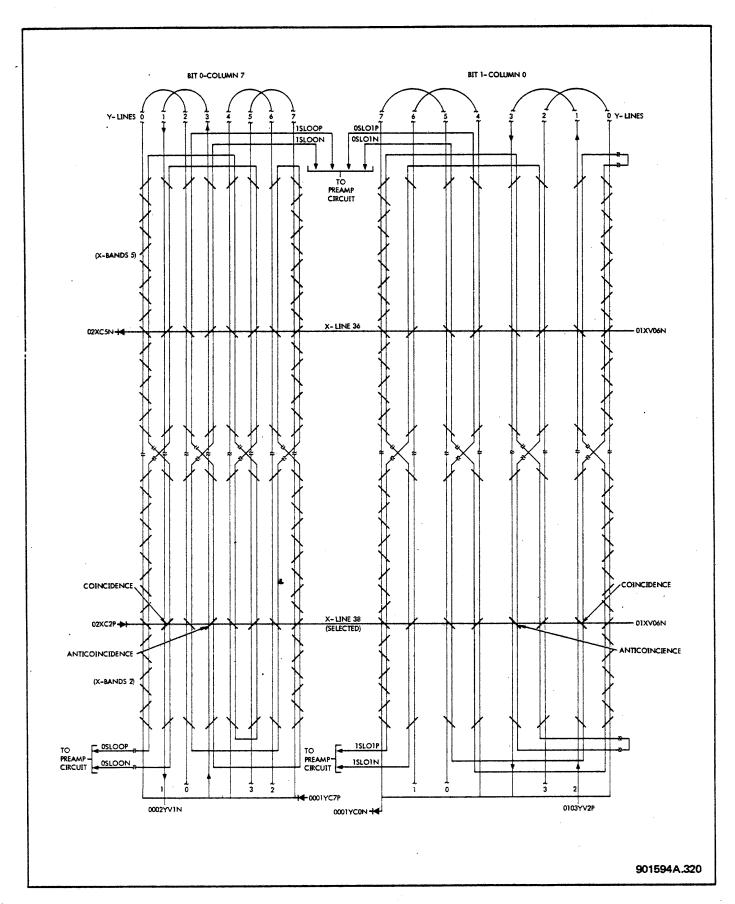

# 3-13. APRIORITY-NORMAL False